# Improved Forward Topologies for DC-DC Applications with Built-in Input Filter

Ching-Shan Leu

Dissertation submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Electrical Engineering

F. C. Lee, Chairman

**Dushan Boroyevich**

Fred Wang

Ming Xu

Tao Lin

January 24, 2006 Blacksburg, Virginia

Keywords: PWM, Forward converter, current ripple reduction, current ripple cancellation, embedded filter, notch filter, low-pass filter

# Improved Forward Topologies for DC-DC Applications with Built-in Input Filter

Ching-Shan Leu Fred C. Lee, Chairman (ABSTRACT)

Among PWM power conversion topologies, the single-switch forward topology is the one that has been most widely used for decades. Its popularity has been based on many factors, including its low cost, circuit simplicity and high efficiency.

However, several issues need to be addressed when using the forward converter such as the core reset, the voltage spikes caused by the transformer leakage inductance, and the pulsating input current waveform.

The transformer is driven in a unidirectional fashion in the forward converter; a tertiary forward converter (TFC) is an example of this. Therefore, the third winding and reset diode must be provided with an adequate period of reset time so that the flux can be fully reset by the end of each switching cycle to prevent core saturation.

Also, due to the utilization of a transformer, leakage inductances cannot be avoided. The energy stored in the leakage inductance during current ramp-up is not transferred to the load, and is not recovered during its discharge phase. As a result, the  $V_{DS}$  waveform has a voltage spike and undesirable high-frequency oscillation. Therefore, a higher voltage-rating switch should be used to reduce the risk of high-voltage breakdown. Although a switch with amply high voltage ratings is available, it would tend to have a

higher on-resistance,  $R_{DS(ON)}$ , resulting in increased conduction losses. Moreover, selection of a switch with higher voltage ratings than necessary may needlessly increase the cost of the design.

Usually an additional circuit such as a snubber circuit or a clamp circuit or the softswitching technique is used to absorb these voltage spikes. Consequently, the leakage inductance is intentionally minimized in the PWM power conversion technique so that it will not degrade the circuit performance. In contrast, the leakage inductance of the transformer may enhance rather than detract from circuit performance with a resonant power conversion technique.

To date, however, no single-switch forward converter has been claimed to be able to enhance the converter performance with the PWM power conversion technique by utilizing the leakage inductance. Therefore, research on the utilization of the transformer leakage inductance in the PWM forward converter is needed. Two techniques, input current ripple reduction and an embedded filter, are proposed to enhance the performance of forward converter using the PWM technique.

By inserting a capacitor between two primary windings of the TFC, an input current ripple reduction technique is proposed and a forward converter with ripple reduction (FRR) is presented in this research work. Because the voltage of the capacitor is clamped to input voltage, the capacitor becomes a second voltage source to share part of the load current. As a result, the input current ripple is reduced. Moreover, the capacitor voltage is clamped both at the static and dynamic states; thus the excessive voltage stress on the main switch  $S_1$  of the FAC during low-line to high-line step transient is eliminated.

Furthermore, without an external LC filter, the EMI noise levels can be further reduced as a result of the embedded notch filter formed by the transformer leakage inductance and clamp capacitor if the notch frequency is designed to be the same as the switching frequency. With the help of the clamp capacitor, therefore, the leakage inductance can enhance rather than detract from the converter performance.

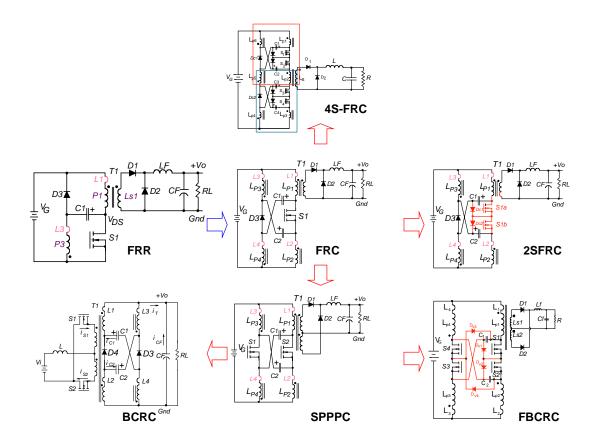

The input current ripple can be reduced further by employing the proposed techniques. Two sets of the clamp capacitors and the leakage inductances are utilized, and the current ripple can even be cancelled if the condition is met. Consequently, the input current becomes a non-pulsating waveform and a forward converter with ripple cancellation (FRC) is presented. Moreover, without an external LC filter, the EMI noise levels can be further attenuated as a result of the embedded low-pass filter formed by the transformer leakage inductances and clamp capacitors. Again, the leakage inductance can enhance the converter performance just as the resonant converter does.

In addition to providing the analysis and design procedure, this work verifies the performance of the presented converters, the FRR and the FRC, by the experimental results.

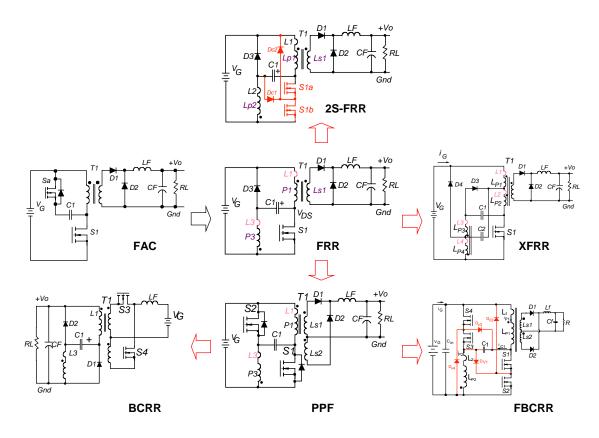

By employing the proposed techniques, eight new topologies have been extended for different power conversion applications. Each member of the FRR and the FRC families is able to enhance the converter performance, in ways such as the elimination of the voltage spikes on the main switch without a snubber circuit and the improvement of the EMI performance with small filter components. Consequently, the cost can be reduced and the space of the converter can be saved.

iv

### Acknowledgements

With sincere appreciation in my heart, I would like to thank my advisor, Dr. Fred C. Lee for his guidance, encouragement and support throughout this work and my studies at Virginia Tech. It was an invaluable learning experience to be one of his students. From him I have learned not only in the knowledge of the power electronics, but also the ability of independent research and the attitude toward research. It is going to benefit me for the rest of my life.

I would also like to thank Dr. Ming Xu for his enthusiastic help during my research at CPES. His valuable suggestions helped to encourage my pursuing this degree.

I am grateful to the other members of my advisory committee, Dr. Dusan Boroyevich, Dr. Fred Wang, and Dr. Tao Lin, for their support, suggestions and encouragement.

Special thanks are due to my previous committee members, Dr. D, Y. Chen, Dr. B. H. Cho, Dr. M. M. Jovanovic, and Dr. Daan Van Wyk for their valuable guidance and suggestions.

I was very fortunate to be able to associate with the incredible faculty, staff and students of CPES. I will cherish the friendships that I have made during my stay here.

I would like to thank the wonderful members of the CPES staff who were always willing to help me out, Ms. Linda Gallagher, Ms. Teresa Shaw, Ms. Marianne Hawthorne, Ms. Michelle Czamanske, Ms. Trish Rose, Ms. Elizabeth Tranter, Ms. Linda Long, Mr. Robert Martin, and Mr. Jamie Evans.

v

It has been a great pleasure to work with the talented, creative, helpful and dedicated colleagues.

I would like to thank all the members and visiting scholar I've studied with during 1988 to 1992: Dr. F. S. Tsai, Dr. R. Ridley, Dr. W. A. Tabisz, Dr. Wei Tang, Dr. Q. Chen, Dr. Gary Hua, Dr. E. Yang, Dr. D. Sable, Dr. R. Farrington, Dr. J. A. Sabate, Dr. A. W. Lotfi, Dr. C. Y. Lin, Dr. Y. Jiang, Dr. N. Dai, Dr. L. Grajales, Dr. V. Vlatkovic, Dr. H. J. Kim, Ms. M. Tullis, Ms. L. Keller, Mr. C. Zhou, Mr. R. Gean, and Mr. D. Tsang.

I would also like to thank all the members and visiting scholar: Dr. Kaiwei Yao, Dr. Jia Wei, Dr. Jinghai Zhou, Dr. Yuancheng Ren, Dr. Shuo Wang, Dr. Yang Qiu, Dr. Xu Yang, Mr. Bing Lu, Mr. Yu Meng, Mr. Doug Sterk, Mr. Kisun Lee, Mr. Julu Sun, Mr. Yan Dong, Mr. Weduo Liu, Mr. Jian Li, Mr. Bin Huang, Mr. Ya Liu, Mr. Yucheng Ying, and Mr. Yi Sun.

I am especially indebted to Dr. Qian Liu and Dr. Ray-Lee Lin. Without their seasonable help, I doubt if I could hang in there and get through all the pain and darkness.

There are some people outside CPES who have made a difference in my life. You may never realize how much your existence means to me. I can't list all your names but you know who you are.

Finally, my deepest and heartfelt appreciation goes to my family, beloved wife Yueh-O Huang, my dear twin boys, and my lovely daughter, with their unconditional love, support, understanding and encouragement for all of my endeavors.

vi

# To my family

## **Table of Contents**

| Acknowle           | edgements v                                                                 |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|

| Table of Contents  |                                                                             |  |  |  |

| Table of Figuresxi |                                                                             |  |  |  |

| List of Ta         | blesxvi                                                                     |  |  |  |

| Chapter 1          | Introduction1                                                               |  |  |  |

| 1.1.               | Background1                                                                 |  |  |  |

| 1.2.               | Comparisons of Efficiency and Voltage Stress                                |  |  |  |

| 1.2.1              | 1. Forward Converter with Resistor-Capacitor-Diode Clamp (RCD)              |  |  |  |

| 1.2.2              | 2. Forward Converter with Active Clamp (FAC)                                |  |  |  |

| 1.2.3              | 3. ZVS Forward Converter with Active Clamp (ZVS-FAC)                        |  |  |  |

| 1.2.4              | 4. Zero-Voltage-Switched Multi-Resonant Forward Converter (ZVS-MRC)         |  |  |  |

|                    |                                                                             |  |  |  |

| 1.2.5              | 5. Clamp-Mode ZVS-MRC                                                       |  |  |  |

| 1.2.0              | 5. Comparison Summary                                                       |  |  |  |

| 1.3.               | Problems of the Forward Converter with Active Clamp (FAC) 16                |  |  |  |

| 1.4.               | Objectives of the Dissertation                                              |  |  |  |

| 1.5.               | Dissertation Organization                                                   |  |  |  |

| Chapter 2          | Forward Converter with Current Ripple Reduction (FRR)                       |  |  |  |

| 2.1.               | Introduction                                                                |  |  |  |

| 2.2.               | Proposed Techniques: Input Current Ripple Reduction and Embedded Filter. 24 |  |  |  |

| 2.3.               | Steady State Analysis                                                       |  |  |  |

| 2.4.               | Operational Principle of the FRR                                            |  |  |  |

| 2.5.               | Input Current Ripple Reduction                                              |  |  |  |

| 2.6.               | Embedded Notch Filter                                                       |  |  |  |

| 2.7.               | Comparisons of the FRR and the FAC                                          |  |  |  |

| 2.8.        | Experimental Validation                                                    |

|-------------|----------------------------------------------------------------------------|

| 2.9.        | Summary                                                                    |

| Chapter 3   | Forward Converter with Current Ripple Cancellation (FRC)                   |

| 3.1.        | Introduction                                                               |

| 3.2.        | Derivation of the Forward Converter with Current Ripple Cancellation (FRC) |

|             |                                                                            |

| 3.2.        | 1. Conditions for Current Ripple Cancellation                              |

| 3.3.        | Steady-State Analysis                                                      |

| 3.4.        | Operational principle of the Forward Converter with Current Ripple         |

| Cance       | llation (FRC)                                                              |

| 3.5.        | Embedded Low-Pass Filter                                                   |

| 3.6.        | Experimental Validation                                                    |

| 3.7.        | Summary                                                                    |

| Chapter 4   | 4 Improvements and Extensions of the Current Ripple Reduction and          |

| Current H   | Ripple Cancellation Converters                                             |

| 4.1.        | Introduction                                                               |

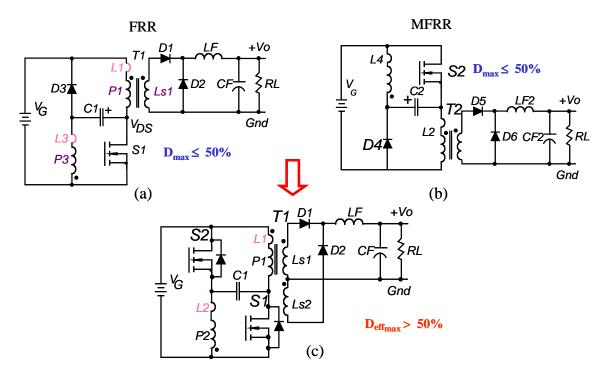

| 4.2.        | Efficiency Improvement by Extending Duty Cycle Scheme                      |

| 4.2.        | 1. Extended Duty Cycle Forward Converter with Current Ripple Reduction     |

| (XF         | <b>TRR</b> )                                                               |

| 4.2.        | 2. Push-Pull Forward Converter (PPF)                                       |

| 4.2.        | 3. Symmetrical Push-Pull Power Converter (SPPPC)                           |

| 4.3.        | Efficiency Improvement by Reducing Voltage Stress                          |

| 4.3.        | 1. Two-Switch Forward Converter with Current Ripple Reduction (2S-FRR)     |

|             |                                                                            |

| 4.3.        | 2. Two-Switch Forward Converter with Current Ripple Cancellation (2S-      |

| FRO         | C)                                                                         |

| 4.3.        |                                                                            |

| 4.3.        | 3. Four-Switch Forward Converter with Current Ripple Cancellation (4S-     |

| 4.3.<br>FR0 |                                                                            |

|             |                                                                            |

| 4.4.      | 1. Full-Bridge Converter with Current Ripple Reduction (FBCRR)    | 102 |

|-----------|-------------------------------------------------------------------|-----|

| 4.4.2     | 2. Full-Bridge Converter with Current Ripple Cancellation (FBCRC) | 105 |

| 4.5.      | Topology Extensions for Isolated Boost Converters                 | 108 |

| 4.6.      | Summary                                                           | 112 |

| Chapter 5 | 5 Conclusions and Future Works                                    | 115 |

| 5.1.      | Conclusions                                                       | 115 |

| 5.2.      | Future Works                                                      | 120 |

| Reference | es                                                                | 122 |

| Vita      |                                                                   | 130 |

# **Table of Figures**

| Fig. 1-1 (a) Circuit diagram and (b) key current waveforms of the TFC with an input I              | LC  |

|----------------------------------------------------------------------------------------------------|-----|

| filter                                                                                             | . 2 |

| Fig. 1-2 Forward converter with RCD clamp reset circuit.                                           | .4  |

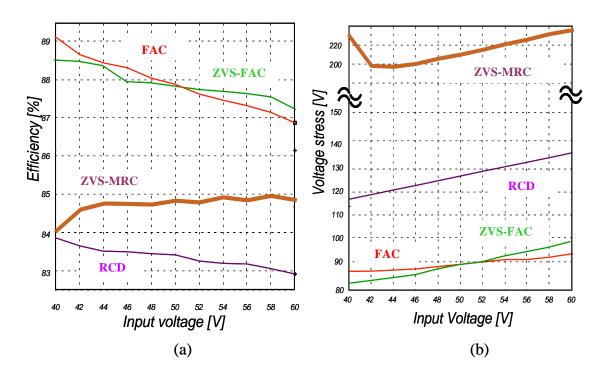

| Fig. 1-3 (a) Measured efficiency and (b) measured voltage stress of the RCD forward                | ırd |

| converter                                                                                          | . 6 |

| Fig. 1-4 Forward converter with active clamp (FAC).                                                | . 7 |

| Fig. 1-5 Comparisons of the (a) measured efficiency (b) measured voltage stress betwee             | en  |

| the FAC and the RCD                                                                                | . 8 |

| Fig. 1-6 Comparisons of the (a) measured efficiency (b) measured voltage stress of t               | he  |

| RCD, the FAC, and the ZVS-FAC.                                                                     | 10  |

| Fig. 1-7 Efficiency comparison between the FAC and the ZVS-FAC for the off-li                      | ne  |

| applications /courtesy of G. Hua [15]                                                              | 10  |

| Fig. 1-8 Forward converter with ZVS-MRC.                                                           | 11  |

| Fig. 1-9 Comparisons of the (a) measured efficiency (b) measured voltage stress of t               | he  |

| RCD, the FAC, the ZVS-FAC, and the ZVS-MRC                                                         | 12  |

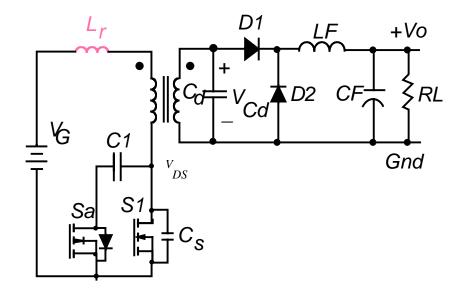

| Fig. 1-10 Circuit diagram of the clamp-mode ZVS-MRC                                                | 13  |

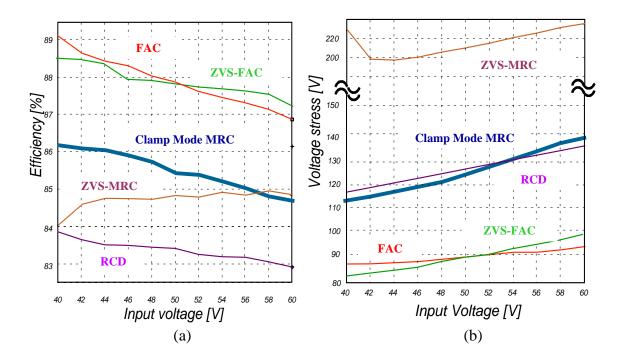

| Fig. 1-11 Comparisons of the (a) measured efficiency (b) measured voltage stress of t              | he  |

| RCD, the FAC, the ZVS-FAC, the ZVS-MRC, and the clamp-mode ZVS-MRC                                 | 14  |

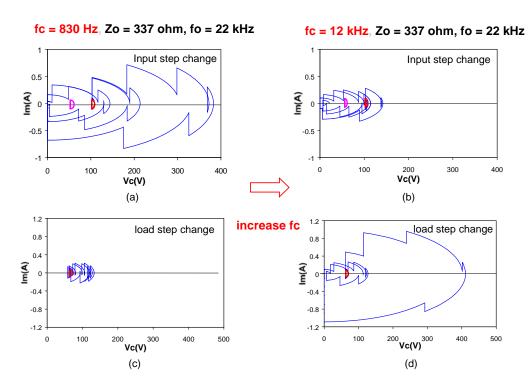

| Fig.1-12 Effect of bandwidth of the close loop control, fc. In line transient, a larger fc h       | ias |

| smaller current stresses and voltage stress; in load transient, a smaller fc has small             | ler |

| current stresses and voltage stress /courtesy of Q. Li [25]                                        | 17  |

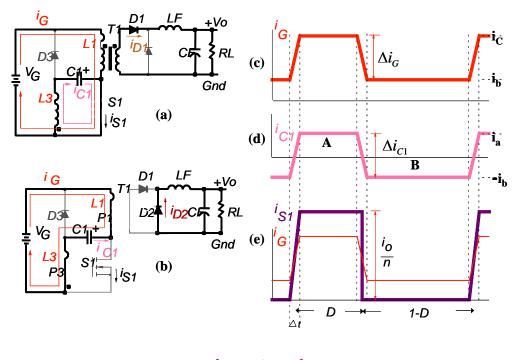

| Fig. 2-1 Circuit diagrams of (a) the TFC, (b) the FRR, $V_{\rm DS}$ of (c) the TFC, and (d) t      | he  |

| FRR                                                                                                | 25  |

| Fig. 2-2. (a) Circuit diagram of the FRR (b) input-voltage step change from $40 \text{ V}$ to $60$ | V,  |

| (c) $V_{DS}$ waveform during the transient ( $L_1 = L3 = 540$ nH, $C_1=20.9$ uF). (d) zoom         | in  |

| V <sub>DS</sub> waveform.                                                                          | 26  |

| Fig. 2-3 Circuit diagram of the proposed converter and the current ripple distribution of                  |

|------------------------------------------------------------------------------------------------------------|

| the currents $i_G$ , $i_{C1}$ , and $i_{S1}$                                                               |

| Fig. 2-4. Evolution of the embedded notch filter technique                                                 |

| Fig. 2-5. Operational modes of the FRR during (a) the on time and (b) the off time, key                    |

| current waveforms (c) input current $I_G$ , (d) capacitor current $I_{C1}$ with its charge                 |

| balance operation, A=B, (e) switch current $I_{S1}$ , $I_{S1}=I_G+I_{C1}$                                  |

| Fig. 2-6 (a) Circuit diagram and (b) key waveforms of the FRR                                              |

| Fig. 2-7 Equivalent circuits of the operating stage of the FRR                                             |

| Fig. 2-8 (a) Equivalent circuit diagram of the FRR and (b) transfer gain of the notch filter               |

| with three different ratios of $L_1$ to $L_3$                                                              |

| Fig. 2-9 Input current $i_G$ of (a) the FRR without employing notch filter feature (b) FRR                 |

| employing notch filter feature (c) comparison of the harmonic component of the two                         |

| cases                                                                                                      |

| Fig. 2-10. Input current waveforms, $i_G$ , of (a) the FAC and (d) the FRR                                 |

| Fig. 2-11 Simulation results of the input current i <sub>G</sub> harmonic components of the FAC and        |

| the FRR                                                                                                    |

| Fig. 2-12 Key current waveforms,(a)-(a') $i_{in}$ , (b)-(b') $i_{Cin}$ and (c)-(c') $i_G$ , of the FAC and |

| the FRR                                                                                                    |

| Fig. 2-13 Circuit diagram of (a) FAC (b) FRR (c) input-voltage step change from 40 V to                    |

| 60 V, $V_{DS1}$ transient waveforms of (d) the FAC ( $L_m$ =80uH, $C_1$ =0.015uF) and (e) the              |

| FRR $(L_1 = L_3 = 540 \text{nH}, C_1 = 20.9 \text{uF})$                                                    |

| Fig. 2-14 (a) Open loop control to output bode plot of (a) the flyback-forward converter                   |

| and (b) the push-pull forward converters /courtesy of Xunwei Zhou [68]                                     |

| Fig. 2-15.Simulation results of the input current $i_G$ harmonic components of the FAC, the                |

| FRR, and the FRR with notch filter                                                                         |

| Fig. 2-16 (a) Notch filter measurement set up and (b) measured transfer gain of the notch                  |

| filter                                                                                                     |

| Fig. 2-17. Key experimental waveforms of the prototype FRR                                                 |

| Fig. 2-18. Comparisons of the measured (a) input current waveforms and (b) their                           |

| fundamental components of the FAC and the FRR                                                              |

| Fig. 2-19. Measured efficiency comparison of the FRR and the FAC                                           |

| Fig. 3-1 Pulsating input current waveforms of (a) the FAC $$ (b) the FRR (c) desired non-                         |

|-------------------------------------------------------------------------------------------------------------------|

| pulsating waveform of the FRC55                                                                                   |

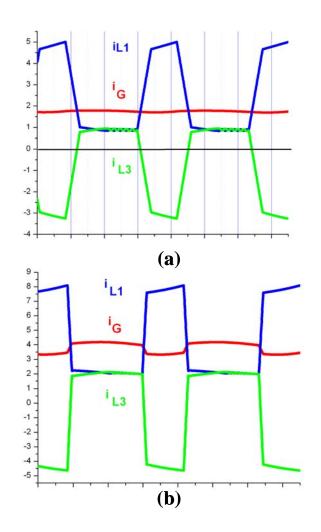

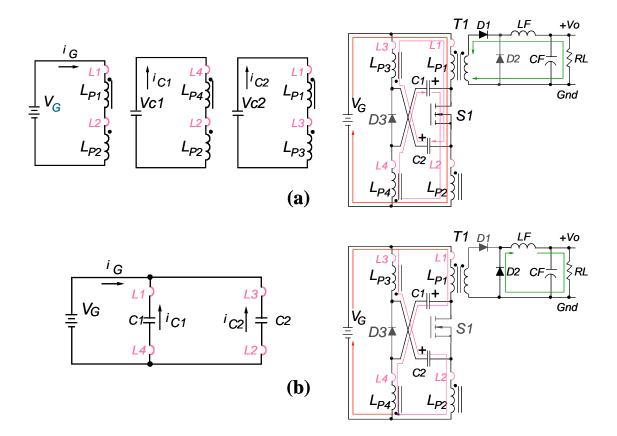

| Fig. 3-2 Circuit diagram of (a) the FRR, (b) the MFRR, and (c)-(e) current ripple                                 |

| cancellation mechanism, $i_G=i_{L1}+i_{L3}(f)$ the proposed FRC                                                   |

| Fig. 3-3 Equivalent circuit diagram for load current ripple distribution during $S_1$ turn-on                     |

| transition                                                                                                        |

| Fig. 3-4 Simulation verification of (a) current ripple cancellation with $L_1=L_4=10uH$ and                       |

| $L_2=L_3=1uH$ , (b) degraded to current ripple reduction performance if 10% deviation                             |

| between $L_1$ and $L_4$ or $L_2$ and $L_3$ ( $L_1=L_2=1.1uH$ and $L_3=L_4=1uH$ )                                  |

| Fig. 3-5 Operating modes of the FRC during (a) the on time (b) the off time 60                                    |

| Fig. 3-6. Current waveforms, (a) $I_{\rm G},$ (b) $I_{\rm C1},$ and $I_{\rm C2}$ , charge balance A=B, (c) switch |

| current I <sub>S1</sub> of the FRC                                                                                |

| Fig. 3-7 (a) Circuit diagram and (b) key waveforms of the FRC                                                     |

| Fig. 3-8 Equivalent circuits of the FRC operating stage                                                           |

| Fig. 3-9 Evolution of the FRC with an embedded low-pass filter                                                    |

| Fig. 3-10 (a) Circuit diagram of the low-pass filter derivation of the FRC, (b) Transfer                          |

| gain of the embedded low-pass filter71                                                                            |

| Fig. 3-11 Input current harmonic comparison of the FAC, the FRR with notch filter and                             |

| FRC                                                                                                               |

| Fig. 3-12 Circuit diagram and key waveforms of the FRC73                                                          |

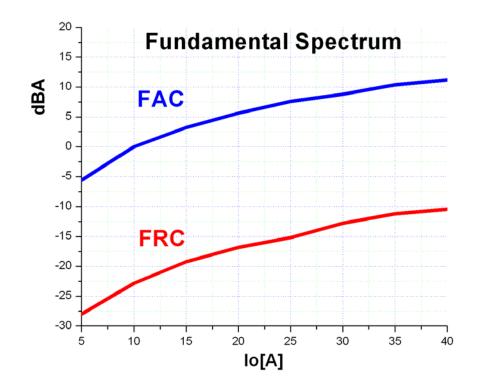

| Fig. 3-13 Measured fundamental component of the input current $i_G$ of the FAC and FRC.                           |

|                                                                                                                   |

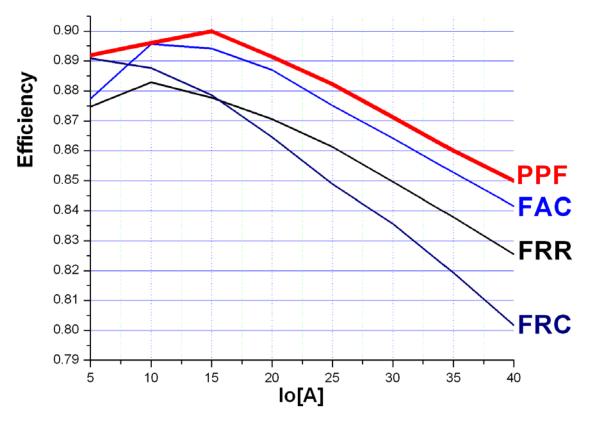

| Fig. 3-14 Measured efficiency comparison of the three tested converters                                           |

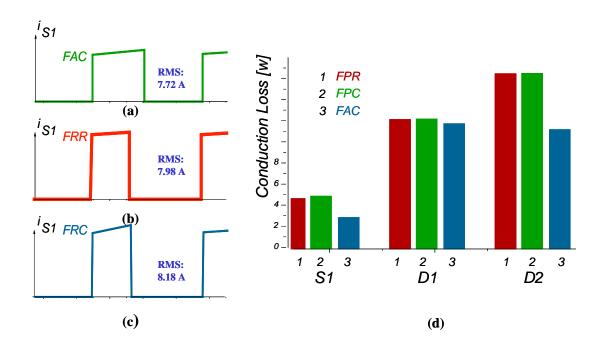

| Fig. 4-1 Circuit diagram of (a) the FRR and (b) the FRC, the operating maximum duty                               |

| cycles are limited to 50% due to the reset voltage being equal to the input voltage. 77                           |

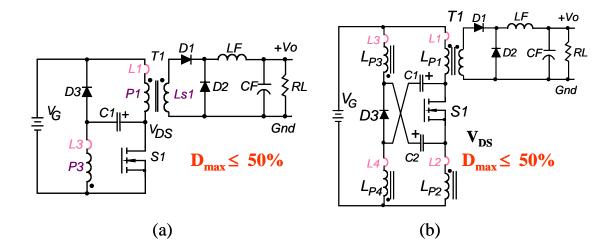

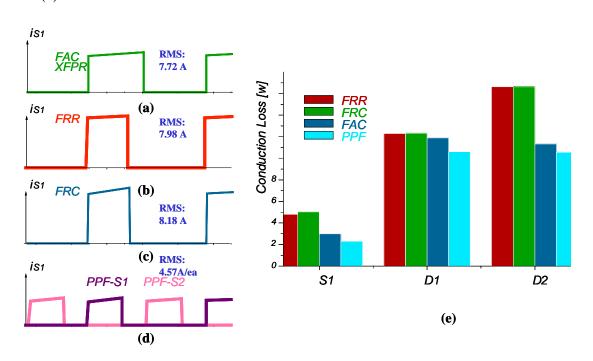

| Fig. 4-2 Comparisons of the (a) RMS switch current $i_{\rm S1}$ and (b) semiconductor devices                     |

| loss breakdown of the FRR, the FRC, and FAC78                                                                     |

| Fig. 4-3 (a) Circuit diagram and (b) key waveforms of the FRR with extended duty cycle.                           |

|                                                                                                                   |

| Fig. 4-4 (a) Equivalent circuit of the FRR notch filter and (b) equivalent circuit of the   |

|---------------------------------------------------------------------------------------------|

| XFRR notch filter (c) notch filter transfer gain of the FRR and (d) notch filter            |

| transfer gain of the XFRR                                                                   |

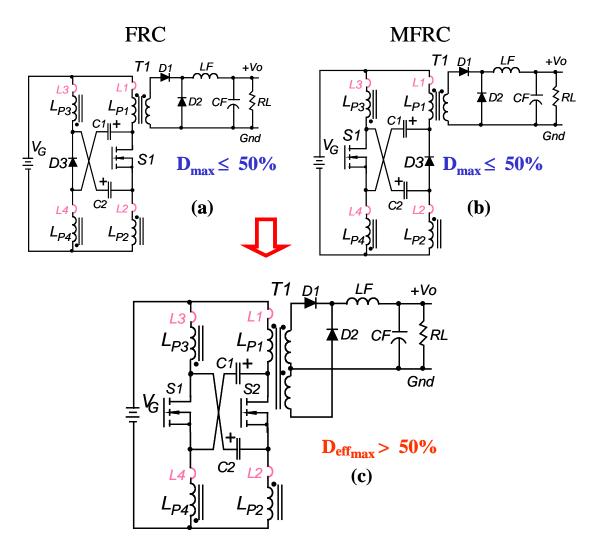

| Fig. 4-5 Circuit diagrams of (a) the FRR and (b) the MFRR and the derivation of (c) the     |

| PPF                                                                                         |

| Fig. 4-6 Comparisons of the (a)-(d) RMS switch current $i_{S1}$ and (e) semiconductor       |

| devices loss breakdown of the FRR, the FRC, FAC, and the PPF                                |

| Fig. 4-7 (a) Measured efficiency comparison and (b) modified efficiency comparison          |

| with compensating LC filter loss of the four tested converters                              |

| Fig. 4-8 Circuit diagrams of (a) the FRC and (b) the MFRC, and the evolution of (c) the     |

| symmetrical push-pull power converter                                                       |

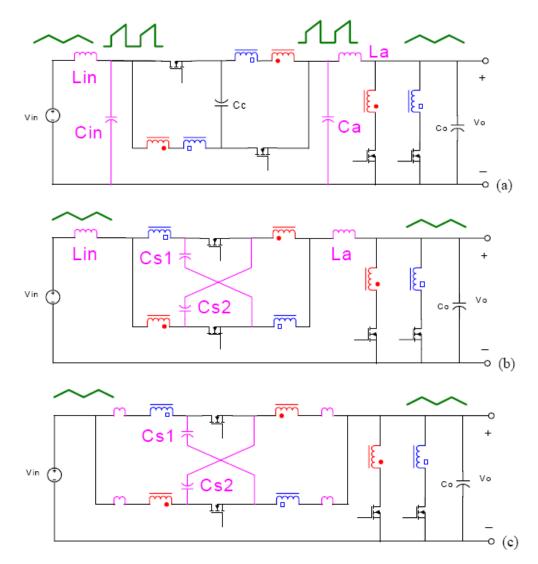

| Fig. 4-9 Integration of L-C filters in multiphase coupled buck converter: (a) with          |

| additional L-C filters, (b) capacitor shifting, and (c) inductor shifting / courtesy of     |

| Peng Xu [71]                                                                                |

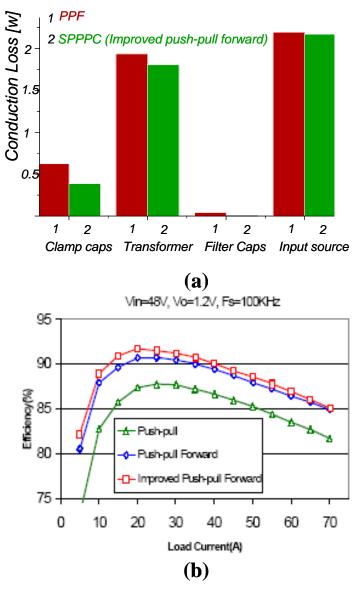

| Fig. 4-10 (a) Loss breakdown and (b) efficiency comparison between the PPF and              |

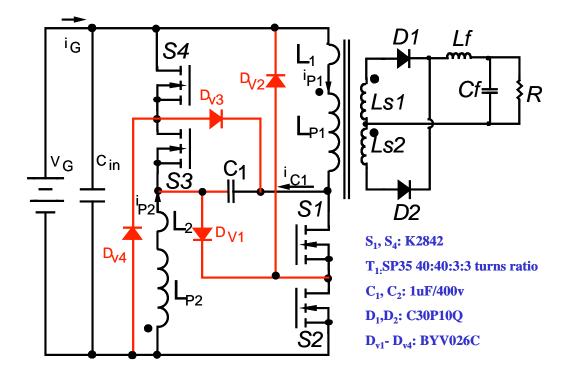

| improved push-pull forward converter / courtesy of Peng Xu [71]                             |

| Fig. 4-11 Circuit diagram of (a) the FRR and (b) the FRC, the MOSFET suffers from           |

| 2V <sub>G</sub> voltage stress in both converters                                           |

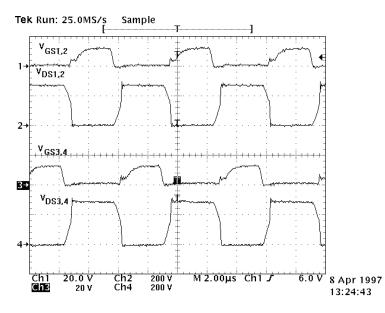

| Fig. 4-12 (a) Circuit diagram of the FRR and (b) the 2S-FRR is derived by employing the     |

| series-connected devices technique                                                          |

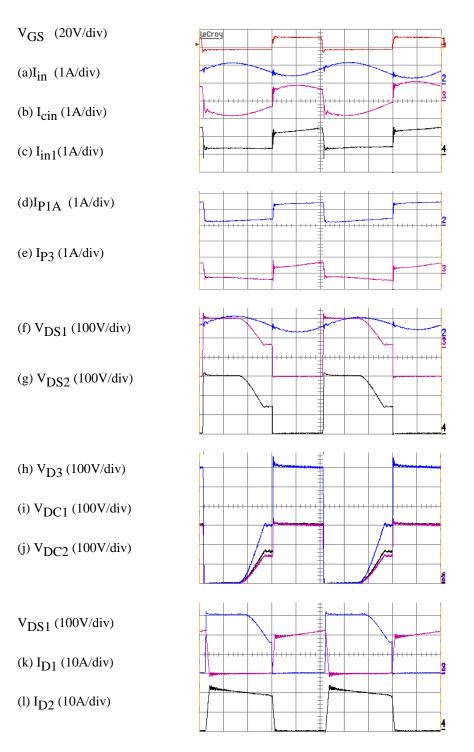

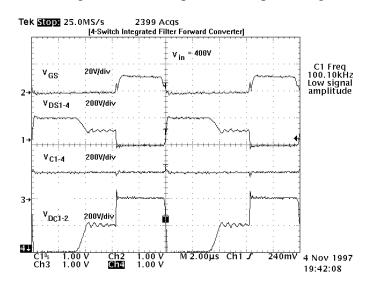

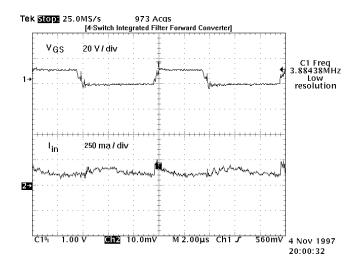

| Fig. 4-13 Oscillograms of the 2S-FRR                                                        |

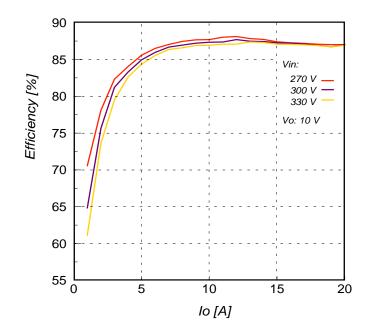

| Fig. 4-14 Measured efficiency of the power stage of the prototype 2S-FRR                    |

| Fig. 4-15 (a) Circuit diagram of the FRC (b) the derivation of the 2S-FRC                   |

| Fig. 4-16 Measured key waveforms of the prototype of the 2S-FRC                             |

| Fig. 4-17 Circuit diagram of (a) the 2S-FRC and (b) the 4S-FRC                              |

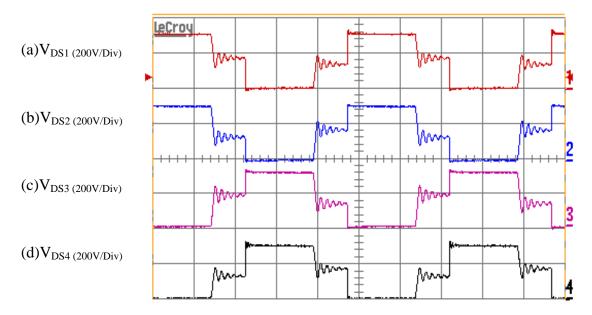

| Fig. 4-18 $V_{DS}$ waveforms of the 4S-FRC, each switch is clamped and shared to $V_G/2100$ |

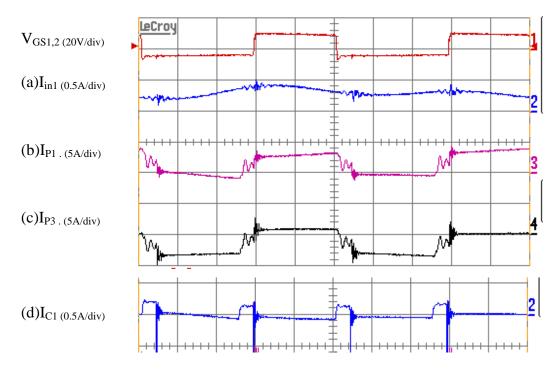

| Fig. 4-19 Gate drive signal and voltage waveforms of the 4S-FRC 101                         |

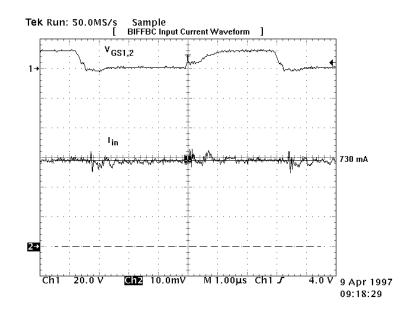

| Fig. 4-20 Gate drive signal and input current waveforms of the 4S-FRC                       |

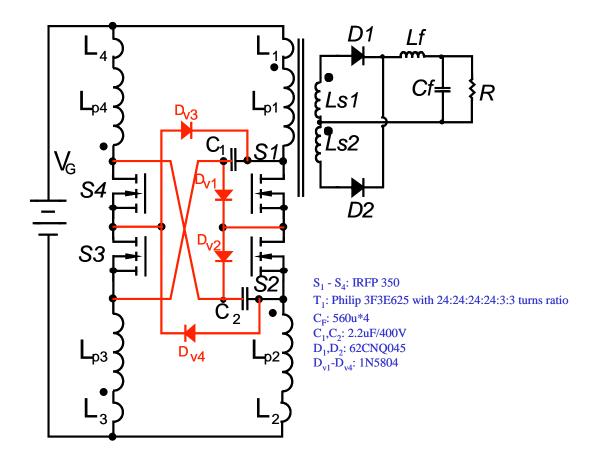

| Fig. 4-21 Circuit diagram and key components used in the full-bridge converter with         |

| current ripple reduction (FBCRR)                                                            |

| Fig. 4-22 Current waveforms of the power stage of the FBCRR                                 |

| Fig. 4-23 Voltage waveforms of the power stage of the FBCRR 105                          |  |  |

|------------------------------------------------------------------------------------------|--|--|

| Fig. 4-24 Circuit diagram and key components used in the full-bridge converter with      |  |  |

| current ripple cancellation (FBCRC)106                                                   |  |  |

| Fig. 4-25 Gate drive signals and $V_{DS}$ of the FBCRC                                   |  |  |

| Fig. 4-26 Gate drive signals and the input current waveform of the FBCRC 108             |  |  |

| Fig. 4-27 Turn-on voltage waveform of the FBCRC                                          |  |  |

| Fig. 4-28 Circuit diagrams of (a) the PPF, (b) bilateral inversion of the PPF 110        |  |  |

| Fig. 4-29 Circuit diagram and key waveforms of the boost converter with ripple reduction |  |  |

| (BCRR)                                                                                   |  |  |

| Fig. 4-30 (a) Circuit diagram of the SPPPC, (b) the circuit diagram and (c) key          |  |  |

| waveforms of the boost converter with ripple cancellation (BCRC)113                      |  |  |

| Fig. 5-1 Circuit diagrams of the FAC and the family tree of the FRR                      |  |  |

| Fig. 5-2 Circuit diagrams of the FRR and the family tree of the FRC                      |  |  |

## List of Tables

Table 2-1 Design specification and components used in the prototype of the FRR ....... 49

### **Chapter 1** Introduction

#### 1.1. Background

Among PWM power conversion topologies, the single-switch forward topology is the one that has been most widely used for decades. Its popularity has been based on many factors, including its low cost, circuit simplicity and high efficiency.

However, several issues need to be addressed when using the forward converter These include the core reset, the voltage spikes caused by the transformer leakage inductance, and the pulsating input current waveform.

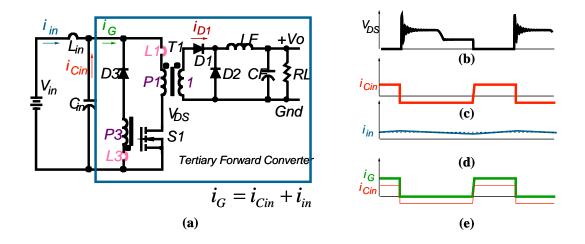

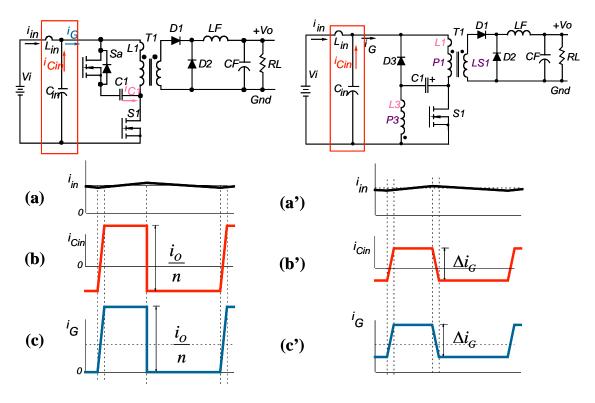

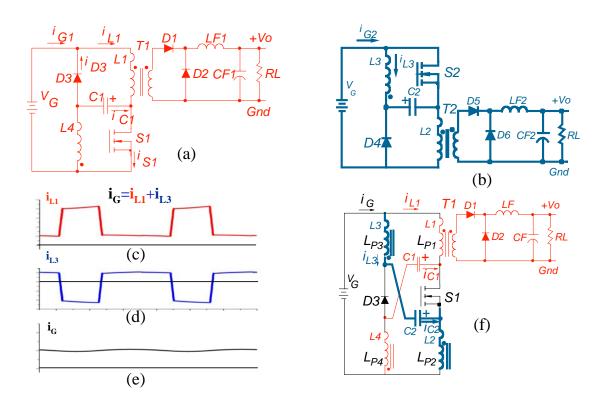

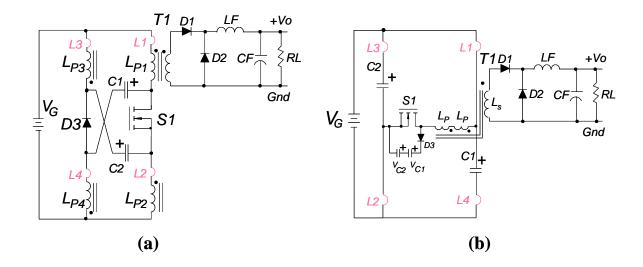

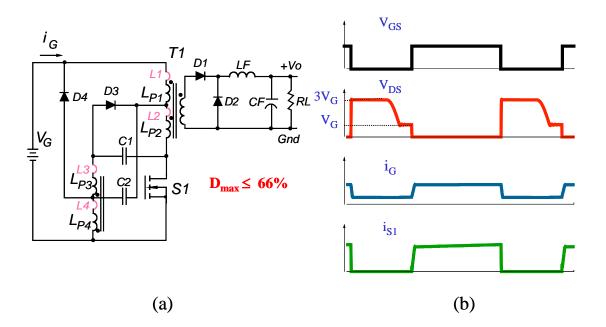

The transformer is driven in a unidirectional fashion; a tertiary forward converter (TFC) is given as an example (Fig. 1-1(a)). Therefore, the third winding,  $L_{P3}$ , and reset diode,  $D_3$ , must be provided with an adequate period of reset time so that the flux can be fully reset by the end of each switching cycle to prevent core saturation.

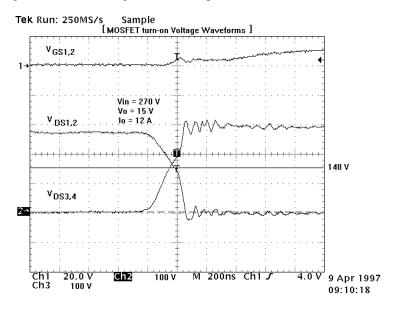

Also, due to the utilization of a transformer, the leakage inductances ( $L_1$  and  $L_3$ ) cannot be avoided. The energy stored in the leakage inductance during current ramp-up is not transferred to the load, and is not recovered during its discharge phase. As a result, the  $V_{DS}$  waveform has a voltage spike and undesirable high-frequency oscillation, as illustrated in Fig. 1-1(b). Therefore, a higher voltage-rating switch should be used to reduce the risk of high-voltage breakdown. Although a switch with amply high voltage ratings is available, it would tend to have a higher on-resistance,  $R_{DS(ON)}$ , resulting in increased conduction losses. Moreover, selection of a switch with higher voltage ratings than necessary may needlessly increase the cost of the design.

Usually either an additional circuit, such as a snubber circuit or a clamp circuit, is added or the soft-switching technique is used to absorb this voltage spike. Consequently, the leakage inductance is intentionally minimized in the PWM power conversion technique so that it will not degrade the circuit performance. In contrast, the leakage inductance of the transformer may enhance rather than detract from circuit performance with a resonant power conversion technique.

To date, however, there is no single-switch forward converter that has been claimed to be able to enhance the converter performance with the PWM power conversion technique by utilizing the leakage inductance. Consequently, further research on the utilization of the transformer leakage inductance in the PWM forward converter is needed.

Due to the nature of the buck converter, the forward converter has a pulsating input current,  $i_G$ , as illustrated in Fig. 1-1(e). This input current creates high-frequency electromagnetic interference (EMI), which disturbs the operation of nearby digital and communication equipment. Reduction of such noise is required for the design to comply with international standards.

Fig. 1-1 (a) Circuit diagram and (b) key current waveforms of the TFC with an input LC filter.

Therefore, an external LC filter formed by the line parasitic inductance,  $L_{in}$ , and the filter capacitor,  $C_{in}$ , is mandatory; their addition is shown in Fig. 1-1(a). This is done so that the high-frequency switching current,  $i_{Cin}$ , is supplied by the input filter capacitor instead of coming from the input source, as shown in Fig. 1-1(b). The intensity of the EMI seen from the power source can be significantly reduced. Accompanied by additional common mode (CM) and differential mode (DM) filters, the converter can meet international EMI regulations.

However, only a few of the other problems inherent in the forward converter, such as core saturation, voltage spike, and switching loss problems have gained much attention by the proposed forward topologies in the existing literature [1]-[61].

In contrast, the problems caused by the pulsating input current have been ignored and no forward converter has been claimed to provide an effective solution without an external LC filter.

Therefore, the exploration of a comprehensive solution for achieving a better performance of the converter is the motivation of the current research work.

This dissertation provides background information about dealing with the abovementioned issues in existing forward converters. Based on the results of the strategies used to deal with these problems, desired features for a forward converter are articulated. By utilizing the clamp capacitor and the transformer leakage inductance, input current ripple reduction and embedded filter techniques are proposed so that the PWM converter performance can be enhanced.

3

#### **1.2. Comparisons of Efficiency and Voltage Stress**

Because the single-switch forward converters proposed in the existing literature are focused on solving some of the inherent problems of the converter such as core saturation, voltage spike, and switching loss problems [1]-[61], the voltage stress and converter efficiency become key parameters to be watched for their impact on performance. Several forward converters with various reset schemes, including a forward converter with a Resistor-Capacitor-Diode clamp (RCD), a forward converter with an active clamp (FAC), a ZVS forward converter with an active clamp (ZVS-FAC), a ZVS Multi-Resonant Converter (ZVS-MRC) and a clamp-mode ZVS-MRC, are reviewed and compared below.

## 1.2.1. Forward Converter with Resistor-Capacitor-Diode Clamp (RCD)

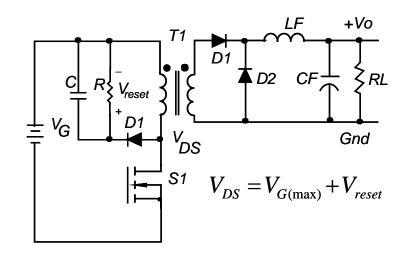

A forward converter with a resistor-capacitor-diode (RCD) clamp circuit is illustrated in Fig. 1-2 [4]-[5]. The reset circuit is composed of a diode and the parallel connection of a resistor and capacitor, which in turn are parallel with the transformer.

Fig. 1-2 Forward converter with RCD clamp reset circuit.

After the switch has been turned off, the diode in the clamp circuit begins to conduct. Thus a negative reset voltage, consisting of the voltage across the clamp capacitor, is provided to reset the transformer.

Without the reset winding and the additional snubber circuit, the reduction of the transformer's cost and the protection of the switch from voltage spike are the advantages of this reset circuit.

The reset voltage is independent of the input voltage [5].

$$V_{reset} \neq f(V_G)$$

Eq. 1-1

Thus, the maximum voltage stress is the sum of the high input voltage and the fixed reset voltage, as shown in Eq. 1-2. Consequently, this reset scheme is more suitable than the tertiary reset scheme for wide-input-range applications.

$$V_{DS} = V_G + V_{reset}$$

Eq. 1-2

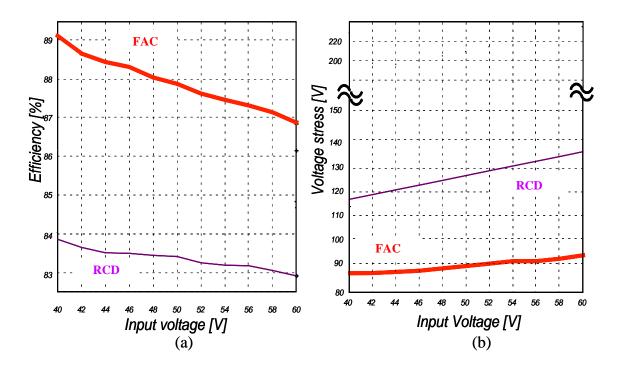

It should be noted, however, that the RCD clamp circuit does not recycle the leakage energy stored in the clamp capacitor. Instead, the charge balance of the capacitor is maintained with the dissipative clamp resistor, resulting in a decrease in efficiency of performance, as shown in Fig. 1-3(a). It would be desirable to improve the converter efficiency by recovering the leakage energy and the forward converter, which can be done with the active clamp (FAC) introduced next.

Fig. 1-3 (a) Measured efficiency and (b) measured voltage stress of the RCD forward converter.

#### **1.2.2.** Forward Converter with Active Clamp (FAC)

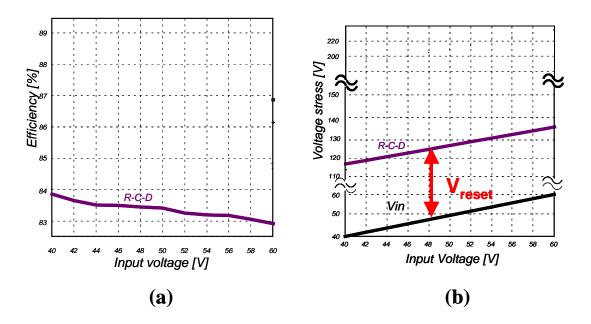

Fig. 1-4 shows the circuit diagram of the forward converter with an active clamp [8]-[19]. The auxiliary switch (S<sub>a</sub>) is used to replace the diode and the resistor in the RCD clamp in order to recycle leakage energy.

The voltage across the clamp capacitor,  $V_{C1}$ , provides the reset voltage during the off time interval, and it can be derived according to the volt-second balance of the transformer.

$$V_{C1} = V_{reset} = f(V_G, D) = \frac{DV_G}{1 - D} = \frac{nV_o}{1 - D}$$

Eq. 1-3

Eq. 1-3 illustrates that the reset voltage decreases as the operating duty cycle decreases for a constant output voltage due to the increment of the line voltage. Additionally, the voltage across the switch  $V_{DS}$  can be derived as the following equation.

$$V_{DS} = V_G + V_{reset} = \frac{V_G}{1 - D}$$

Eq. 1-4

Since the input voltage increases while the operating duty cycle decreases,  $V_{DS}$  tends to remain approximately constant over a certain input voltage. Consequently, this reset scheme features the lowest voltage stress on the main switch  $S_1$  in the steady state.

Instead of being dissipated, as is the case with the RCD clamp circuit, the energy stored in the transformer leakage inductance is recycled to the input source. Consequently, the power loss is reduced and the switch is protected from a voltage spike. In addition, due to the charge balance of the clamp capacitor, the flux of the transformer is almost symmetrical in the first and third quadrants. Therefore, this topology utilizes the transformer most efficiently.

The FAC has 5% efficiency improvements and lower voltage stress than the RCD, as shown in Fig. 1-5.

Fig. 1-4 Forward converter with active clamp (FAC).

Fig. 1-5 Comparisons of the (a) measured efficiency (b) measured voltage stress between the FAC and the RCD.

It is desirable to operate the converter with zero-voltage-switching (ZVS) for highfrequency high input-voltage applications. ZVS operation of the FAC can be easily achieved, which will help to attain a higher power density, as discussed next.

#### **1.2.3. ZVS Forward Converter with Active Clamp (ZVS-FAC)**

To achieve ZVS, the energy stored in the leakage and magnetizing inductances,  $L_{LK}$  and  $L_m$ , must be large enough to provide the capacitive energy demands of the MOSFET output capacitances.

$$\frac{1}{2}L_m i_m^2 + \frac{1}{2}L_{LK} i_{\Pr i}^2 \ge \frac{1}{2}C_r (V_G + V_{cr})^2$$

Eq. 1-5

where Cr is the total resonant capacitance, and the combination of the two MOSFET output capacitors are in parallel with the transformer primary capacitance. The magnetizing current,  $i_m$ , is totally dependent on the transformer design, a function of the

ferrite material permeability and number of turns. Leakage inductance is affected by the winding design and technique, and the output load current reflected to the primary. Due to the light load, the leakage energy will go towards zero. Therefore, the magnetizing inductance is the more significant energy to achieve ZVS.

Consequently, ZVS operation of the FAC can be achieved by simply adding a gap in the transformer to reduce the magnetizing inductance or increase the peak magnetizing current [14].

However, the price to be paid for achieving ZVS is the increased conduction loss of the switch. The primary conduction losses of the ZVS-FAC are approximately 35% higher than the FAC.

The merits of the ZVS-FAC can be summarized as listed below.

- 1. Low switching losses and low switching noise;

- 2. Minimum voltage stress of the main switch; and

- 3. Maintenance of ZVS for the entire load range and line range.

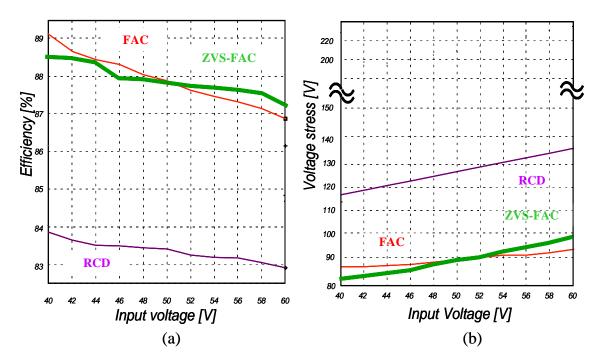

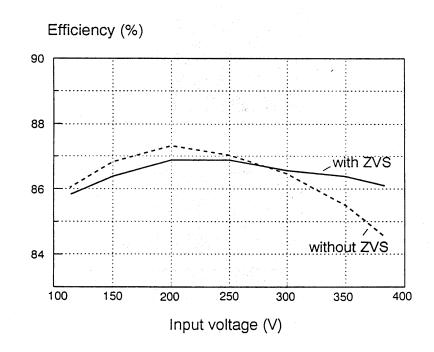

However, the switch loss improvements cannot compensate for the increased conduction loss under the low line operating conditions as shown in Fig. 1-6(a). In contrast with to the FAC, the efficiency improvements are only achieved above the nominal line operating conditions. Another efficiency study for the off-line applications shows the same tendency as illustrated in Fig. 1-7 [15]. It can be concluded that the FAC has good efficiency performance and the soft-switching operation is an optional feature for some applications.

Fig. 1-6 Comparisons of the (a) measured efficiency (b) measured voltage stress of the RCD, the FAC, and the ZVS-FAC.

Fig. 1-7 Efficiency comparison between the FAC and the ZVS-FAC for the off-line applications /courtesy of G. Hua [15].

## 1.2.4. Zero-Voltage-Switched Multi-Resonant Forward Converter (ZVS-MRC)

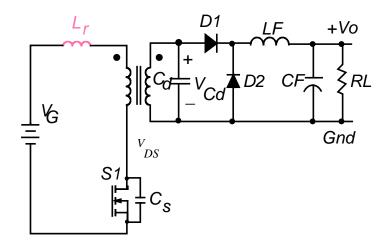

The circuit diagram of the forward ZVS-MRC is shown in Fig. 1-8. The ZVS-MRC was proposed to achieve optimum soft-switching performance for all semiconductor devices in the power circuit [16]. All the major parasitic components, including the MOSFET output capacitance, diode junction capacitance, and the transformer leakage inductance, are absorbed into the resonant circuit. ZVS of the MOSFET and diode is obtained by shaping the voltage waveforms across the switches so that the device voltage returns to zero before turn-on.

Fig. 1-8 Forward converter with ZVS-MRC.

However, by allowing resonance of the output capacitance of the switch, voltage stress across the MOSFET is three to four times the input voltage. This limits the use of the single-ended ZVS-MRC in off-line applications. Furthermore, conduction loss of the MOSFET is also increased when higher-voltage-rating devices are used.

The forward ZVS-MRC has an inherent automatic reset mechanism due to the interactions between the magnetizing inductance and the secondary-side capacitor. The

volt-second across  $C_d$  is equal to the volt-second applied to the transformer. If the net volt-second applied to the transformer is positive during one cycle, it will cause the magnetizing current to increase. This increment of the magnetizing current will cause  $C_d$ to be charged more negatively during the next cycle, which will subsequently decrease the magnetizing current. This automatic reset mechanism eliminates the need for an external reset circuit.

The performance of the forward ZVS-MRC is shown in Fig. 1-9.

Fig. 1-9 Comparisons of the (a) measured efficiency (b) measured voltage stress of the RCD, the FAC, the ZVS-FAC, and the ZVS-MRC.

Although it operates with zero-voltage switching, the efficiency is not good enough to be compared to the FAC for the following reasons.

1. The presence of the circulating currents, which are caused by the resonance due to the resonant capacitor on the secondary side, results in power dissipation in the transformer and MOSFET. 2. The voltage stress on the MOSFET is higher than in PWM converters resulting in an increased conduction loss.

Also, another disadvantage is the constant off-time control that makes it difficult to optimize the magnetic components.

#### 1.2.5. Clamp-Mode ZVS-MRC

Fig. 1-10 shows the circuit schematic of the clamp-mode forward ZVS-MRC [17]. By employing a soft-switching, non-dissipative active clamp network, the performance of the ZVS-MRC can be significantly improved. The clamping action is obtained by placing a series combination of an active switch and a capacitor in parallel with the power MOSFET, so that the voltage across the main switch is clamped to a lower value as shown in Fig. 1-11. The proposed clamping switch also operates with zero voltage by allowing its anti-parallel diode to conduct before turn-on. Due to the lower voltage stress, the clamp-mode forward ZVS-MRC is more efficient than the MRC.

Fig. 1-10 Circuit diagram of the clamp-mode ZVS-MRC.

Fig. 1-11 Comparisons of the (a) measured efficiency (b) measured voltage stress of the RCD, the FAC, the ZVS-FAC, the ZVS-MRC, and the clamp-mode ZVS-MRC.

#### **1.2.6.** Comparison Summary

Because the single-switch forward converters proposed in the existing literature are focused on solving some of the problems inherent in the forward converter, such as core saturation, voltage spike, and switching loss problems, the voltage stress and converter efficiency become key values to be compared for impact on performance and has been detailed in [14]. Please refer to Fig. 1-11, which is the summary of the performance comparison.

The RCD has the lowest efficiency due to the dissipation of the leakage energy. The conventional MRC experiences the highest voltage stress on the main switch (up to four times the input voltage). Although it is operated in ZVS, the increased conduction losses make the efficiency of the conventional MRC not very high. In contrast, the FAC has the best performance: the lowest voltage stress and the highest efficiency. Consequently, it is used as a benchmark in this research. The advantages of the FAC are as follows.

- 1. No additional reset winding or dissipative clamps are required for transformer reset;

- 2. Higher maximum duty cycle allows wider input voltage range or higher turns ratio resulting in significant reduction in current stresses on the primary side and voltage stresses on the secondary side;

- The leakage energy can be stored and recycled, resulting in higher efficiency and lower noise;

- Switch voltage is clamped to a controlled level resulting in lower stress switching devices;

- 5. The voltage stress across the switches is relatively constant over the full range of input voltage, which is not available in other single-ended implementations due to the switch voltage stress being proportional to the input voltage.

- 6. The transformer waveforms allow easy implementation of the synchronous switching technique on the secondary side.

However, the FAC requires more components, an additional high-voltage MOSFET clamp switch and an isolated variable-duty-cycle gate drive, rather than the other forward topologies to achieve the advantages listed above.

Recently, it has been widely reported that there will be problems in the FAC if the converter is not properly designed [21] -[24].

Thorough analysis and design trade-offs can be found in [25], but the key problems are briefly described below.

15

## 1.3. Problems of the Forward Converter with Active Clamp (FAC)

The dynamic behavior of the FAC could cause excessive switch voltage stress, transformer saturation, or active clamp switch diode reverse recovery problems if it is not correctly designed [25].

Specifically, before the input-voltage transient, the FAC converter operates with a large duty cycle and with a balanced flux in the core so that  $V_G D = V_{C1}(1-D)$ . Since the duty cycle and the clamp capacitor voltage  $V_{C1}$  do not change instantaneously after the line change, the volt-second product becomes unbalanced, i.e.  $V_G D > V_{C1}(1-D)$ . As a result, the magnetizing current of the transformer starts to increase after the input-voltage change. The increased magnetizing energy charges the clamp capacitor, increasing the clamp-capacitor voltage. This transition continues until  $V_{C1}$  becomes large enough so that the volt-second product becomes  $V_G D < V_{C1}(1-D)$ , and the magnetizing current of the transformer starts to increase after starts to decrease and the subsequent decrease after the transient can be seen as an oscillatory response of the transformer.

In addition to an excessive voltage stress on the primary switch and/or saturation of the core of the transformer, the body diode of auxiliary switch  $S_a$  may conduct due to a positive magnetizing current at the instant when main switch  $S_1$  is turned on. Consequently, the failure of the converter may occur due to a low-impedance current path through the clamp capacitor, the auxiliary-switch body diode, and the main switch.

Moreover, there is an opposite effect with respected to the bandwidth of the control during the load and line transients as illustrated in Fig.1-12(a) - (b) and Fig.1-12(c) - (d), respectively. The bandwidth of the control,  $f_c$ , is increased from 830 Hz to 12 KHz in both cases. During the line transient, a larger  $f_c$  has smaller current stresses and voltage stress; while in load transient, a smaller  $f_c$  has smaller current stresses and voltage stress. Consequently, it becomes an uncertain condition to select proper design parameters.

As a result, the design issues become complicated and an optimal performance of the FAC is hard to achieve. Without providing a clear design guideline, the industry often uses a trial-and-error iteration process in the design of the FAC. This can be timeconsuming and increase cost.

Fig.1-12 Effect of bandwidth of the close loop control, fc. In line transient, a larger fc has smaller current stresses and voltage stress; in load transient, a smaller fc has smaller current stresses and voltage stress /courtesy of Q. Li [25].

#### 1.4. Objectives of the Dissertation

In addition to the voltage stress and converter efficiency, valuable information with respect to the leakage inductance can be obtained from the evaluation of the tested forward converters.

With a resonant power conversion technique, such as the MRC, the circuit requires inductance and capacitance so that the leakage inductance of the transformer can enhance rather than detract from circuit performance.

On the contrary, the leakage inductance energy is either dissipated in the RCD or recycled to the input source in the FAC. Consequently, the leakage inductance is intentionally minimized in the PWM power conversion technique so that it will not degrade the circuit performance.

To date, however, no one has claimed that a single-switch forward converter is able to enhance the converter performance in the PWM power conversion technique by utilizing the leakage inductance. Therefore, it is necessary to research the utilization of the transformer's leakage inductance in the PWM forward converter. This work proposes two techniques, input current ripple reduction and an embedded filter, to enhance performance of the forward converter using PWM technique.

By inserting a capacitor between two primary windings of the TFC, an input current ripple reduction technique is proposed and a forward converter with ripple reduction (FRR) is presented in this research work. Because the voltage of the capacitor is clamped to the input voltage, the capacitor becomes a second voltage source to share part of the load current. As a result, the input current ripple is reduced. Moreover, the capacitor voltage is clamped both at the static and dynamic states, and the excessive voltage stress on the main switch  $S_1$  of the FAC during the low-line to high-line step transient is eliminated.

Furthermore, without an external LC filter, the EMI noise levels can be further reduced as the result of the embedded notch filter formed by the transformer leakage inductance and clamp capacitor if the notch frequency is designed at the switching frequency. With the help of the clamp capacitor, therefore, the leakage inductance can enhance rather than detract from the converter performance.

The current ripple can be further reduced by employing the proposed techniques. Two sets of the clamp capacitor and the leakage inductance are utilized and the current ripple can even be cancelled if the condition is met. Consequently, input current becomes a non-pulsating waveform and a forward converter with ripple cancellation (FRC) is presented. Moreover, without an external LC filter, the EMI noise levels can be further attenuated as a result of the embedded low-pass filter formed by the transformer leakage inductances and clamp capacitors. Again, the leakage inductance can enhance the converter performance like the resonant converter.

In addition to providing the analysis and design procedure, the performance of the presented converters, the FRR and the FRC, are verified with the experimental results.

By employing the proposed techniques, eight new topologies have been extended for different power conversion applications. Each member of the FRR and the FRC families is able to enhance the converter performance by doing such things as the eliminating the voltage spikes on the main switch without a snubber circuit and improving the EMI performance with reduced filter components. Consequently, the cost and the space of the converter can be reduced. The major objectives of this dissertation are as follows.

1. To reduce voltage stress,  $V_{DS}$ , on the main switch  $S_1$  of the FAC during large signal transient.

Among the existing forward converters, the FAC has been regarded to be the best topology. However, it requires an additional high-voltage MOSFET clamp switch and isolated variable-duty-cycle gate drive circuitry which is not necessary with the other forward topologies. Furthermore, the dynamic behavior of the FAC could cause excessive switch voltage stress, transformer saturation, or active clamp switch diode reverse recovery problems if it is designed improperly. Additionally, the opposite impact on the control bandwidth during the line and load transients can confuse the designer. As a result, the design issues become complicated and optimal performance of the FAC is hard to achieve. Without providing a clear design guideline, the industry often uses a trial-and-error iteration process in the design of the FAC. This can increase time spent designing as well as the cost. An important research objective, therefore, is to explore an effective solution to

eliminate the above-mentioned drawbacks of the FAC.

2. To reduce the pulsating input current ripple of the forward converter.

Due to the fact that there is a pulsating input current in the PWM forward converters, an external LC filter must be added. Consequently, some of the limited space is occupied and the cost is increased. In addition, the temperature rise in the filter capacitor due to a larger RMS current affects reliability.

It is important, therefore, to reduce the input current ripple by utilizing the proposed input current ripple reduction and embedded filter techniques to enhance the converter performance without an external LC filter.

3. To achieve a non-pulsating input current ripple of the forward converter without an external LC filter.

Therefore, it is important to take full advantage of the proposed techniques to cancel input current ripple so that a non-pulsating input current can be obtained and the performance of the EMI can be further improved without an external LC filter.

4. To extend the power converter topology for different power conversion applications.

Since the pulsating current occurs at the input port of the PWM buck and buckderived converter, it would be useful to employ the proposed techniques to derive the topology extensions for different power conversion applications.

The overall objective of this dissertation is to explore an effective solution that incorporates the two proposed techniques, input current ripple reduction and embedded filter, to enhance the converter performance. This would result in new converter topologies that would cost less while performing better.

#### 1.5. Dissertation Organization

This dissertation consists of five chapters. In Chapter 1, several types of forward converter are discussed and compared as the background of the research. Several issues such as the core reset, voltage stress, and the accompanying loss are investigated. Among the five tested forward converters, the forward converter with active clamp (FAC) performances best and is taken as the benchmark of the current research work. However, several problems occur in the FAC during a large signal transient. To explore a solution to alleviate the problems of the FAC becomes the motivation of the current research work. Two families of the forward converter are presented to reach this end.

In Chapter 2, two techniques, input current ripple reduction and an embedded filter, are proposed and a forward converter with current ripple reduction (FRR) is presented as the entry-level topology to achieve the research objectives listed above. The operational principle and the features of the topology are described. By utilizing the SABER simulation program, several performance comparisons between the FRR and the FAC are made. The performance of the presented converter is verified with experimental results.

In Chapter 3, by fully taking advantage of the techniques proposed in Chapter 2, a forward converter with current ripple cancellation (FRC) is presented to further improve the converter performance. The operational principle and the features of the FRC are described. In addition, the experimental results are presented.

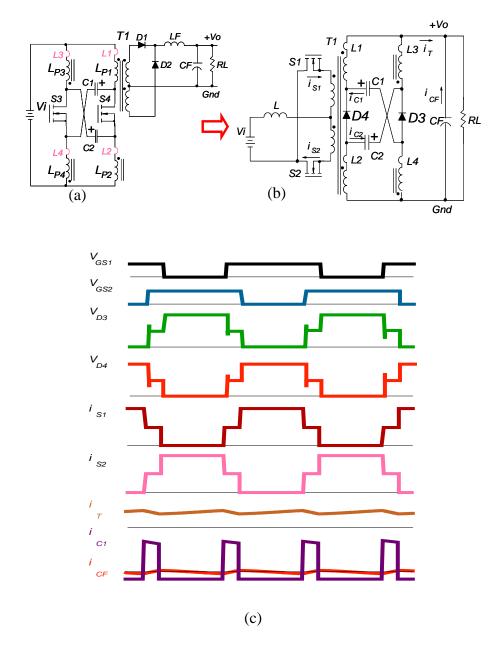

In Chapter 4, several extended topologies of the FRR and FRC are presented. These were created by employing the proposed techniques to enhance the converter performance for different power conversion applications. Moreover, by using a bilateral inversion technique, both ripple reduction and embedded filter techniques can be applied to the isolated PWM boost converter. The output current ripple is thus reduced, and size reduction of the output capacitor is attainable.

The conclusions and the suggestions for the future works are given in Chapter 5.

# Chapter 2 Forward Converter with Current Ripple Reduction (FRR)

#### 2.1. Introduction

Several forward converters have been proposed to solve some of the problems inherent with this forward topology, such as core saturation, voltage spike, and switching loss. Among the forward converters proposed in the literature, the FAC has gained widespread acceptance for many low-to-medium power DC/DC converter applications due to its high efficiency and having the lowest voltage stress.

However, the FAC requires more components, an additional high-voltage MOSFET clamp switch and an isolated variable-duty-cycle gate drive, which the other forward topologies to achieve the advantages listed above do not.

Recently, it has been widely reported that there will be problems with excessive voltage over the switch, diode reverse-recovery problems of the body diode of the clamp switch, or transformer core saturation due to large signal transients if the converter is not properly designed [21] -[24].

As a result, the design issues become complicated and optimal performance of the FAC is hard to achieve. Without a clear design guideline, a trial-and-error iteration process is often used by the industry in the design of the FAC. This can increase the time spent and the cost of the design process.

Furthermore, there is a common characteristic of the buck and buck-derived converters; the input current waveform is a pulsating waveform. The problems caused by

23

this pulsating input current are usually solved by adding an external LC filter. Not only can these filters occupy some of the limited space, but this solution also increases the cost of the converter.

In addition to eliminating the excessive voltage stress of the FAC during the large signal transient, at the same time a comprehensive solution should be able to alleviate the problems caused by both the transformer leakage inductance and the pulsating input current ripple. By utilizing the clamp capacitor and the transformer leakage inductance, two techniques, input current ripple reduction and embedded filter, are thus proposed to enhance the performance of the PWM forward converter.

## 2.2. Proposed Techniques: Input Current Ripple Reduction and Embedded Filter

Two techniques: input current ripple reduction and an embedded filter, are proposed by utilizing the clamp capacitor and the transformer leakage inductance in this research work so that the performance of the PWM forward converter can be enhanced.

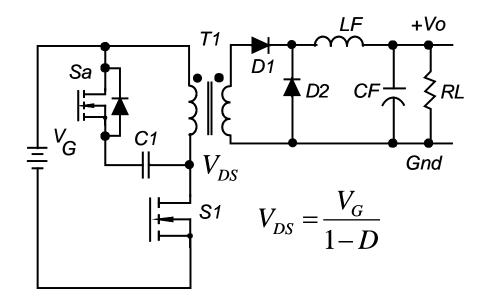

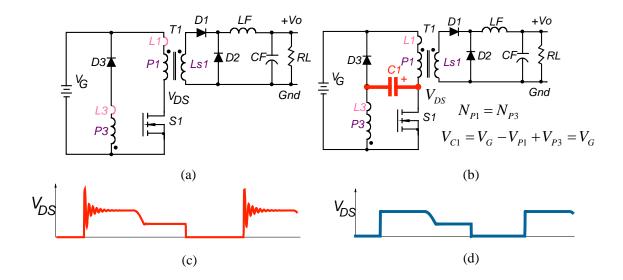

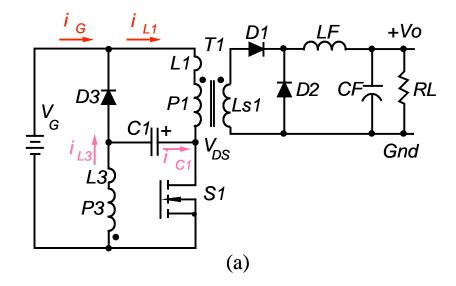

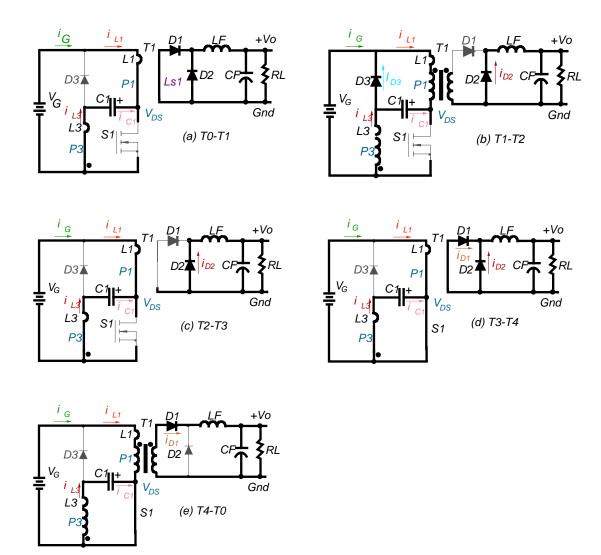

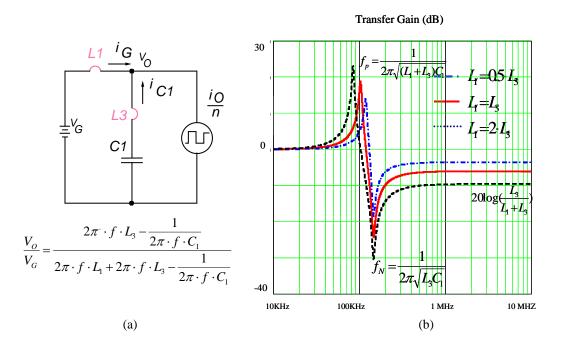

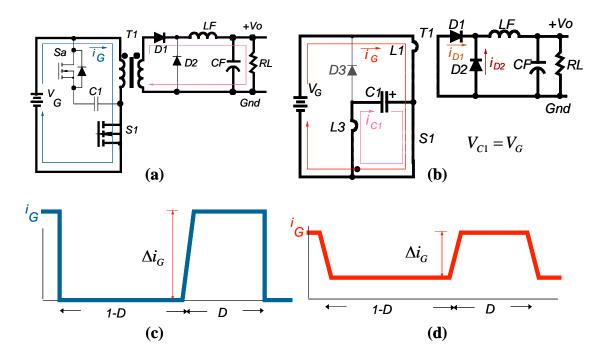

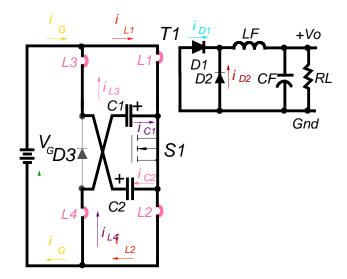

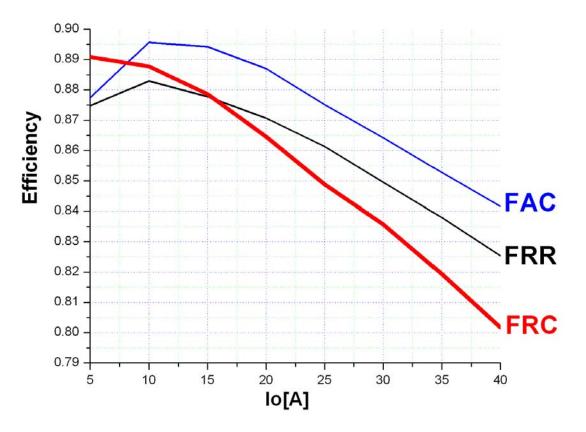

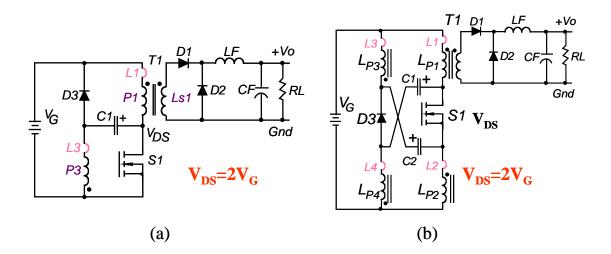

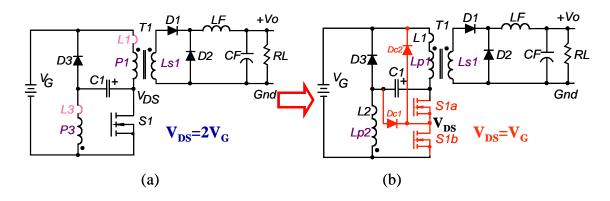

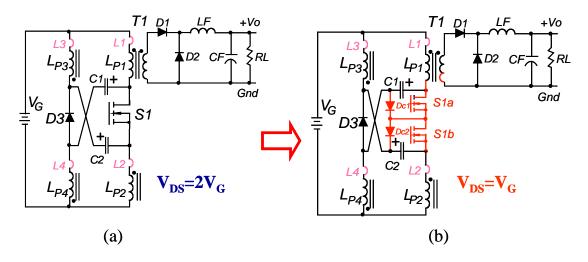

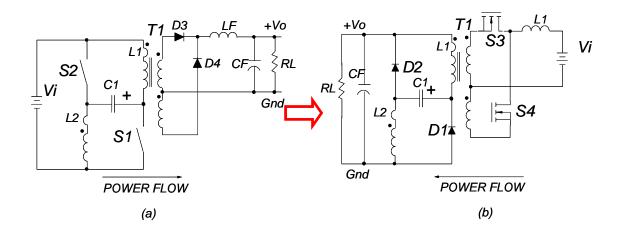

By inserting a capacitor between two primary windings of the TFC (Fig. 2-1(a)), an input current ripple reduction technique is proposed and a forward converter with ripple reduction (FRR) is illustrated in Fig. 2-1(b). In contrast to the TFC (Fig. 2-1(c)), the proposed technique can absorbed the energies of the transformer leakage inductances,  $L_1$  and  $L_3$ , when the main switch  $S_1$  is turned off. As a result, the voltage spikes on the main switch is eliminated as illustrated in Fig. 2-1(d).

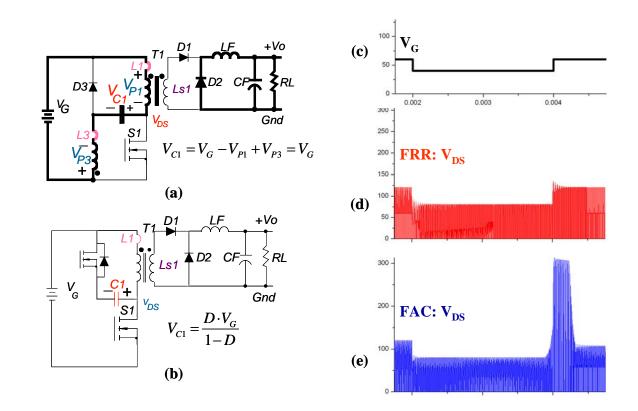

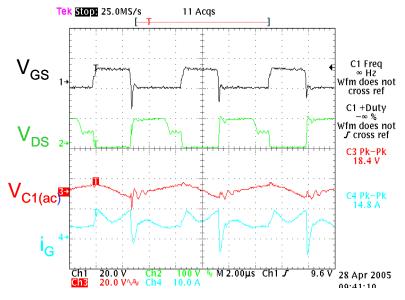

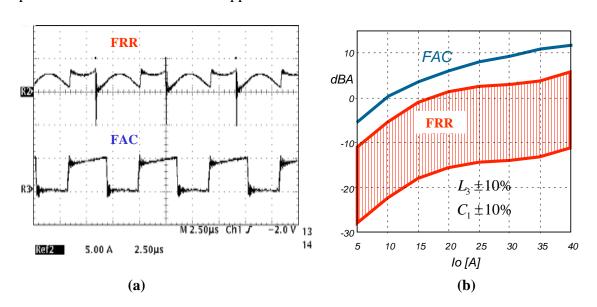

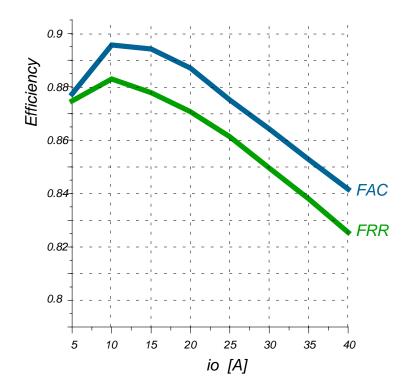

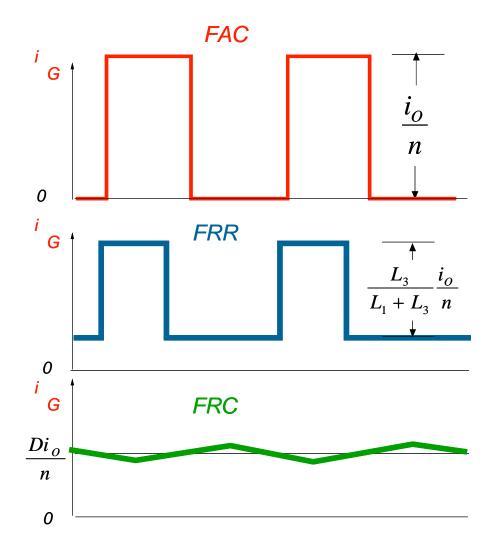

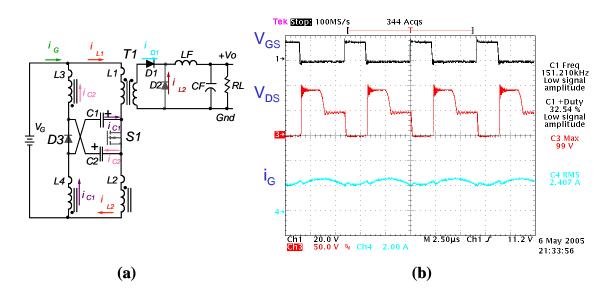

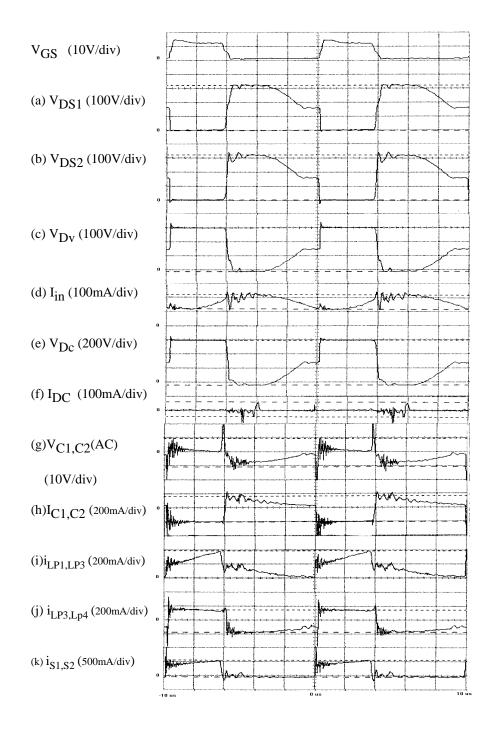

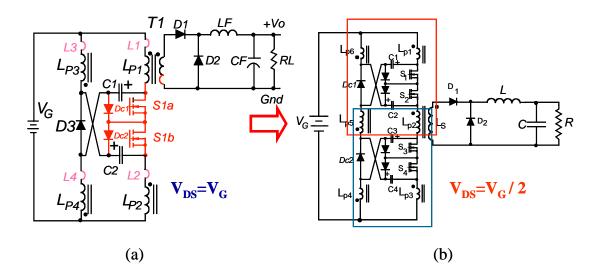

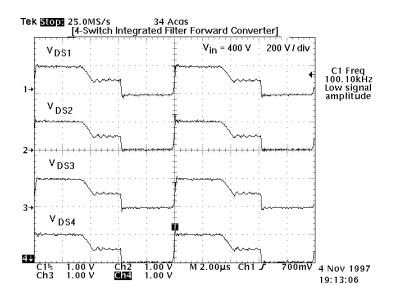

Fig. 2-1 Circuit diagrams of (a) the TFC, (b) the FRR,  $V_{DS}$  of (c) the TFC, and (d) the FRR. As illustrated in Fig. 2-2(a), the primary windings  $P_1$  and  $P_3$  have the same number of turns resulting in the following equation is valid during the off time interval.

$$\left|V_{P1}\right| = \left|V_{P3}\right|$$

Eq. 2-1

Due to the opposite parity of P<sub>1</sub> and P<sub>3</sub>, therefore, the capacitor voltage V<sub>C1</sub> is charged and clamped to input voltage,  $V_G$ , as derived in the following equation.

$$V_{C1} = V_G - V_{P1} + V_{P3} = V_G$$

Eq. 2-2

This is different from the other capacitor voltage clamp schemes; for example, the capacitor voltage of the FAC is governed by the volt-second of the transformer as expressed in the following equation.

$$V_{C1} = \frac{DV_G}{1 - D} = \frac{nV_O}{1 - D}$$

Eq. 2-3

Therefore, the capacitor voltage is the function of the operating duty cycle as well as the input voltage.

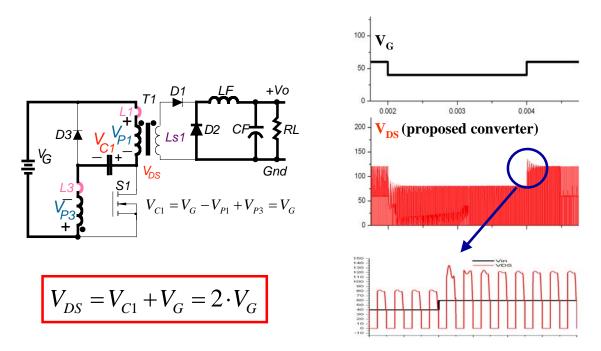

Referring to Eq. 2-2, on the other hand, the capacitor voltage of the proposed technique is clamped to input voltage and it is able to quickly track the input voltage change both at the static and the dynamic transient states as illustrated in **Fig. 2-2**(b) through **Fig. 2-2**(e).

Therefore, the excessive voltage stress on the main switch  $S_1$  of the FAC during low-line to high-line step transient is eliminated.

Fig. 2-2. (a) Circuit diagram of the FRR (b) input-voltage step change from 40 V to 60 V, (c)  $V_{DS}$  waveform during the transient ( $L_1 = L3 = 540$ nH,  $C_1=20.9$ uF). (d) zoom in  $V_{DS}$  waveform.

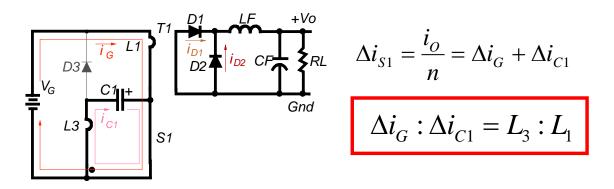

Due to  $V_{C1}=V_G$ , the load currents are thus provided by the  $V_G$  via  $L_1$  and  $V_{C1}$  via  $L_3$ when the main switch is turned on as illustrated in Fig. 2-3. Accompanied with the transformer leakage inductance, the input current ripple can be reduced. The leakage inductance plays a key role in reducing the input current ripple at the main switch turn on instant. The load current flows through the main switch  $S_1$  and the input current ripple,  $\Delta i_G$ , and capacitor current ripple,  $\Delta i_{C1}$ , are derived as the following equations.

$$\Delta i_{S1} = \frac{i_O}{n} = \Delta i_G + \Delta i_{C1}$$

Eq. 2-4

$$\Delta i_{G} = \frac{V_{G}}{L_{1}} \Delta t = \frac{L_{3}}{L_{1} + L_{3}} \frac{i_{O}}{n}$$

Eq. 2-5

$$\Delta i_{C1} = \frac{V_G}{L_3} \Delta t = \frac{L_1}{L_1 + L_3} \frac{i_O}{n}$$

Eq. 2-6

where  $i_0$  is the load current and n is the transformer turns ratio.

The current ripple distribution is dependent on the ratio of the leakage inductances  $L_1$  and  $L_3$  derived from Eq. 2-5 and Eq. 2-6 and expressed in the following equation.

$$\Delta i_G : \Delta i_{C1} = L_3 : L_1$$

Eq. 2-7

Fig. 2-3 Circuit diagram of the proposed converter and the current ripple distribution of the currents  $i_G$ ,  $i_{C1}$ , and  $i_{S1}$ .

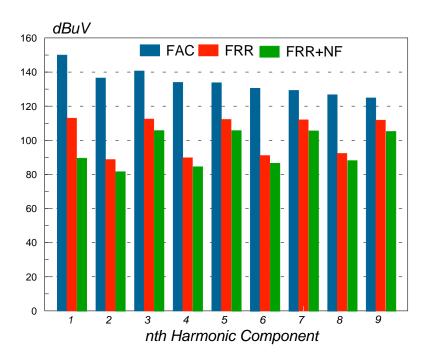

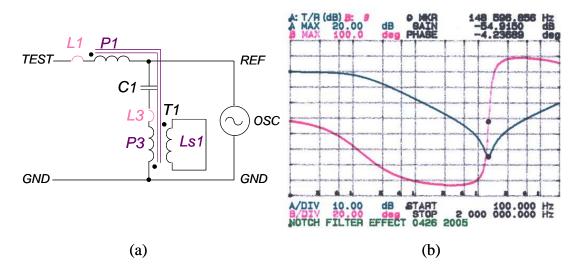

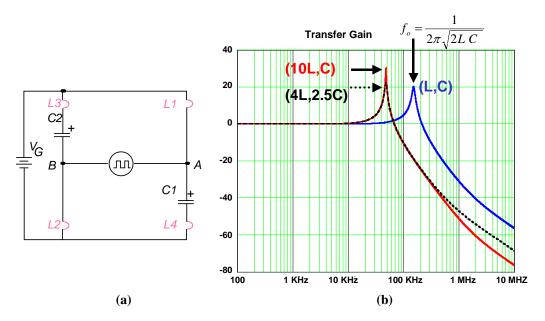

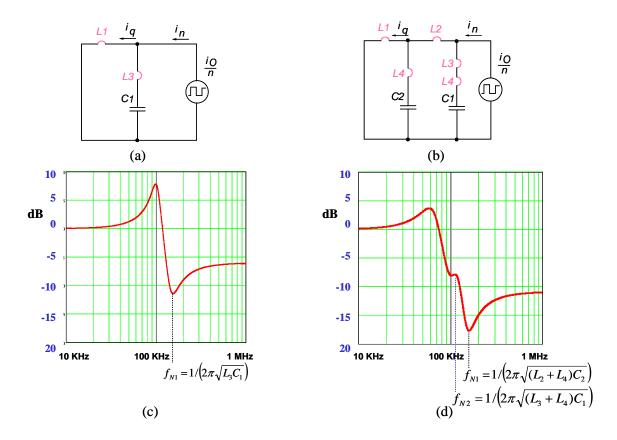

In addition to proposing the input current ripple reduction technique, there is an embedded notch filter technique that can be applied to the PWM forward converter so that the EMI performance can be enhanced.

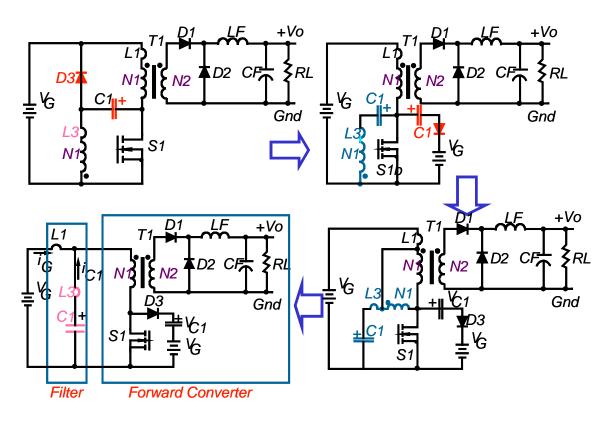

The embedded notch filter technique is illustrated in Fig. 2-4. The derivation begins with shifting the voltage clamp network  $S_1$ - $C_1$ - $D_3$  from Fig. 2-4(a) and the equivalent circuit can be obtained as shown in Fig. 2-4(b). Next, the components are clockwise relocated from  $P_3$ - $L_3$ - $C_1$  to  $C_1$ - $L_3$ - $P_3$ . Due to the fact that they have the same

number of turns and polarity, the transformer primary windings,  $P_1$  and  $P_3$ , can be connected in parallel, as shown in Fig. 2-4(c). Finally,  $P_3$  is merged into  $P_1$  and the circuit of the FRR is equivalent to a filter cascading with a forward converter as shown in Fig. 2-4(d).

Fig. 2-4. Evolution of the embedded notch filter technique.

Consequently, without an external LC filter, the EMI noise levels can be further reduced as the result of the embedded notch filter formed by the transformer leakage inductance and clamp capacitor, if the notch frequency is designed to be the same as the switching frequency. With the help of the clamp capacitor, therefore, the leakage inductance can enhance rather than detract from the converter performance.

### 2.3. Steady State Analysis

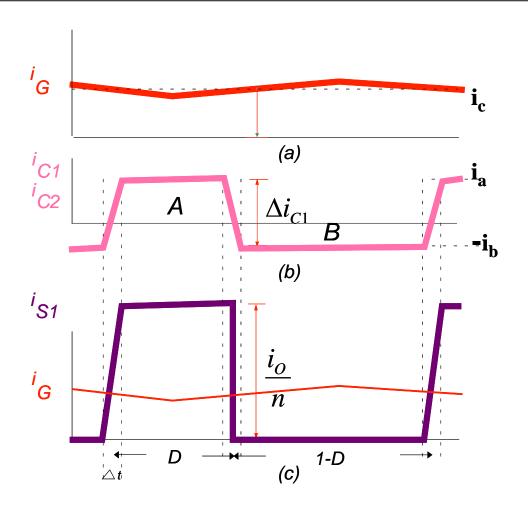

Three key current waveforms, switch current  $i_{S1}$ , the input current  $i_G$ , and the clamp capacitor current  $i_{C1}$ , are quantified as the reference in introducing the operational principle.

The charge balance property of the clamp capacitor is utilized to explore the current ripple reduction feature of the FRR. Illustrated in Fig. 2-5(a) and Fig. 2-5(b) are the operational modes during the on time and the off time of the FRR. As shown in Fig. 2-5(c), Fig. 2-5(d), and Fig. 2-5(e), the switch current,  $i_{S1}$ , the input current,  $i_G$ , and the clamp capacitor current,  $i_{C1}$ , and their current levels are labeled with  $i_a$ ,  $i_b$ , and  $i_c$  during different operating times. In addition, the current ripple distribution between the input source and the clamp capacitor are represented with  $\Delta i_G$  and  $\Delta i_{C1}$ .

Assuming  $i_{mag} \ll i_0$ , where  $i_0$  is the load current, and  $i_{mag}$  is the magnetizing current, the load current is the same as the current that flows through the main switch  $i_{S1}$  during the S<sub>1</sub> turn-on time interval with the following equation.

$$i_G + i_{C1} = i_{S1} = \frac{I_o}{n}$$

Eq. 2-8

$i_{S1} = i_G + i_{C1}$

Fig. 2-5. Operational modes of the FRR during (a) the on time and (b) the off time, key current waveforms (c) input current  $I_G$ , (d) capacitor current  $I_{C1}$  with its charge balance operation, A=B, (e) switch current  $I_{S1}$ ,  $I_{S1}=I_G+I_{C1}$ .

During the  $S_1$  off time interval, the following equation applies.

$$i_G + i_{C1} = i_{S1} = 0$$

Eq. 2-9

The current levels,  $i_a$ ,  $i_b$ , and  $i_c$  can be quantified by employing the charge balance of the capacitor and the Faraday law.

$C_1$  is discharged to the load with  $i_a$  during the on time interval and charged by the input source with  $i_b$  during the off time interval.

Applying the charge balance, A=B, as illustrated in Fig. 2-5 (d),

$$i_a \cdot D = i_b \cdot (1 - D)$$

Eq. 2-10

At the turn-on instant,  $i_G$  and  $i_{C1}$  are linearly charged by the input voltage and the clamp capacitor voltage.

$$\Delta i_{C1} + \Delta i_G = \frac{i_O}{n}$$

Eq. 2-11

$$i_c - i_b = \Delta i_G = \frac{L_3}{L_1 + L_3} \frac{i_O}{n}$$

Eq. 2-12

$$i_a + i_b = \Delta i_{C1} = \frac{L_1}{L_1 + L_3} \frac{i_O}{n}$$

Eq. 2-13

According to Eq. 2-12, the input current ripple value is reduced to  $(\frac{L_3}{L_1 + L_3} \frac{i_0}{n})$  in

the FRR. Comparing to the FAC, the current ripple reduction is with the ratio of  $(\frac{L_3}{L_1 + L_3})$ . Referring to Eq. 2-12 and Eq. 2-13, the current ripples  $\Delta i_G$  and  $\Delta i_{C1}$  are strongly dependent on the ratio of the L<sub>1</sub> to L<sub>3</sub>. The larger the L<sub>1</sub> to L<sub>3</sub> ratio is, the smaller the input current ripple value  $\Delta i_G$  will be, resulting in a reduction of the EMI intensity. However, a larger L<sub>1</sub> to L<sub>3</sub> ratio would increase the RMS current of the clamp capacitor and the voltage stress of the main switch. Moreover, an external inductor would be needed or a special winding scheme should be applied in the construction of the transformer.

From Eq. 2-10 and Eq. 2-13,  $i_a$  and  $i_b$  can be derived as the following equations.

$$i_{a} = \frac{L_{1}(1-D)}{(L_{1}+L_{3})} \frac{i_{o}}{n}$$

Eq. 2-14

$$i_{b} = \frac{DL_{1}}{(L_{1}+L_{3})} \frac{i_{o}}{n}$$

Eq. 2-15

From Eq. 2-12 and Eq. 2-15,  $i_c$  is derived as the following equation.

$$i_c = i_b + \Delta i_G = \frac{DL_1 + L_3}{(L_1 + L_3)} \frac{i_o}{n}$$

Eq. 2-16

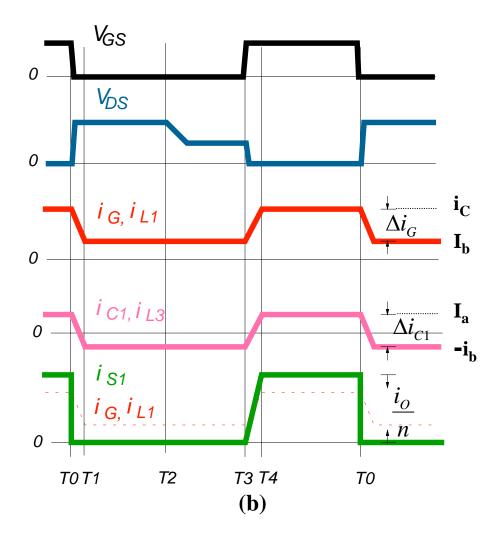

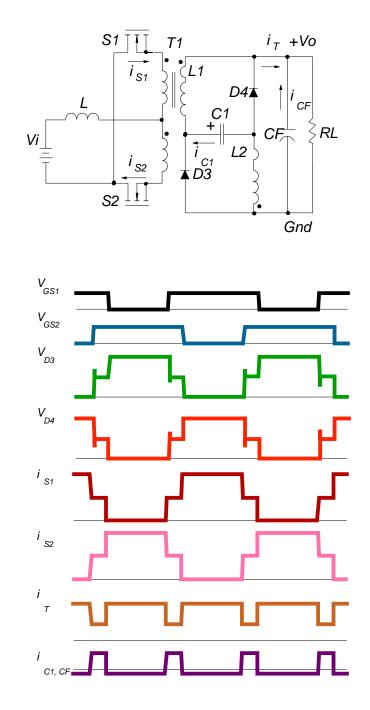

#### 2.4. Operational Principle of the FRR

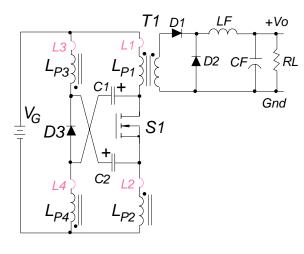

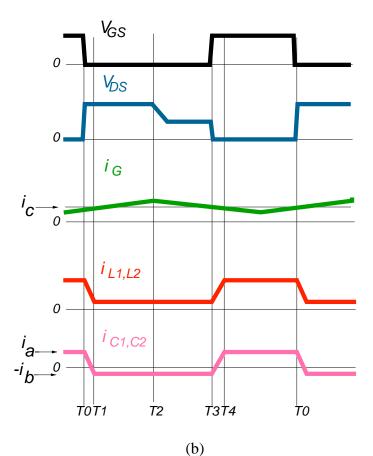

The circuit diagram and key waveforms of the forward converter with current ripple reduction (FRR) are shown in Fig. 2-6. The primary side of the power stage consists of a switch, S<sub>1</sub>, one clamp capacitor, C<sub>1</sub>, one-clamped diode, D<sub>3</sub>, and one transformer. The transformer is comprised of two identical primary windings, P<sub>1</sub> and P<sub>3</sub>, and one secondary winding, L<sub>S1</sub>, with the turns ratio of (n : n : 1). L<sub>1</sub> and L<sub>3</sub> are represented as the leakage inductance of P<sub>1</sub> and P<sub>3</sub>, respectively. To simplify the analysis, the output filter inductance is assumed to be sufficiently large to be approximated by a current source with the value equal to the output current, I<sub>O</sub>. The clamp capacitor, C<sub>1</sub>, is assumed to be sufficiently large that the voltage across it can be assumed to be constant. Also,  $i_{mag} \ll i_O$ , and  $f_o = \frac{1}{2\pi \sqrt{L_3C_1}} \ll f_S$  are assumed, where I<sub>o</sub> is the load current I<sub>mag</sub> is the

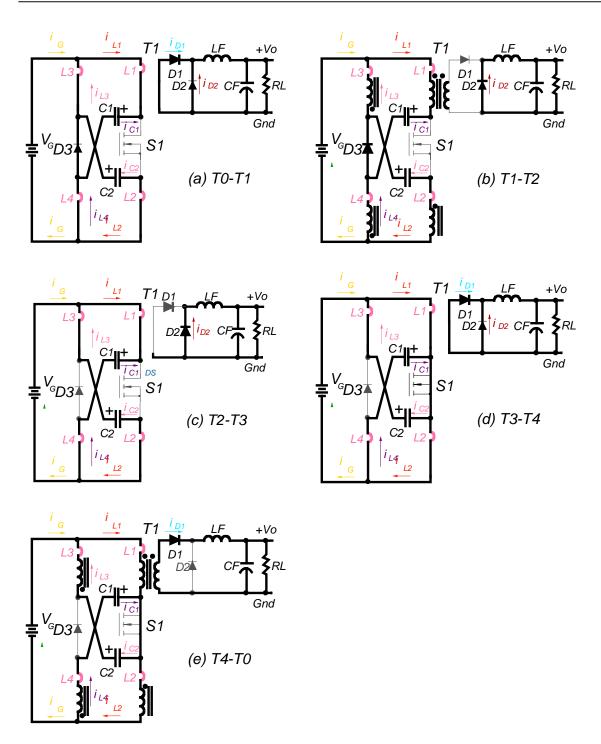

magnetizing current, and  $f_0$  is the natural frequency defined by L<sub>3</sub> and C<sub>1</sub>. During steadystate operation, five operation stages exist within one switching cycle (shown in Fig. 2-7(a)-(e)):

(a)

$$T_0 - T_1$$

:

The circuit operation begins with the switch off at  $T_0$ . Prior to  $T_0$ , the power is transferred from the input source,  $V_G$ , and the energy is stored in capacitor  $C_1$ .  $i_{C1}$  provides part of the load current via  $P_3$ , while  $i_G$  provides the complementary part of the load current via  $P_1$  so that their sum is equal to the reflected load current. According to Eq. 2-14 and Eq. 2-16,

At  $T_0$ ,  $i_G = i_{L1}$ ,  $i_{C1} = i_{L3}$  and  $i_{Mag} \ll i_o$ ,

$$i_G + i_{C1} = \frac{i_O}{n}$$

Eq. 2-17

After  $S_1$  turns off at  $T_0$ , transformer windings  $P_1$ ,  $P_3$  and  $L_{S1}$  are shorted due to the turning on of  $D_1$  and  $D_2$ . Consequently, both leakage inductances  $L_1$  and  $L_3$  are supplied by a negative voltage and thus the currents,  $i_G$  and  $i_{C1}$ , are linearly decreased to the reflect load current interruption as the following equation.

During  $T_0 < t < T_1$ ,

$$i_G = i_{L1} = i_c - \frac{V_G}{L_1} (t - T_0)$$

and Eq. 2-18

$$i_{C1} = i_{L3} = i_a - \frac{V_G}{L_3}(t - T_0)$$

Eq. 2-19

When the voltage across the switch reaches  $2V_G$ , the clamp diode  $D_3$  will be forced to turn on, and the voltage stress  $V_{DS}$  on switch  $S_1$  will be clamped to  $2V_G$ .  $-V_{C1}$ and  $-V_G$  are thus applied on the windings  $P_1$  and  $P_3$  to start the core-reset function.

At  $T_1$ ,  $D_1$  is turned off because load current is freewheeled through diode  $D_2$  and  $i_G$  and  $i_{C1}$  are expressed with following equations.

$$i_G = i_{L1} = i_h$$

Eq. 2-20

$$i_{C1} = i_{L3} = -i_b$$

Eq. 2-21

The time interval,  $T_1$ - $T_0$  can be calculated as

$$T_1 - T_0 = \frac{L_1 L_3}{V_G (L_1 + L_3)} \frac{i_o}{n}$$

Eq. 2-22

Fig. 2-6 (a) Circuit diagram and (b) key waveforms of the FRR.

Fig. 2-7 Equivalent circuits of the operating stage of the FRR.

(b)  $T_1 - T_2$ :

During this time period, the magnetizing current flows through  $D_3$  to provide core reset of the transformer. The primary current  $i_G$  flows through  $L_1$ -P<sub>1</sub>-C<sub>1</sub>-L3-P3. Because the voltages across the windings P<sub>1</sub> and P3 cancel each other due to the presence of the opposite winding polarities, C<sub>1</sub> is charged by the input power source,  $V_G$ . At  $T_2$ , the zero average-volt-second of the transformer is achieved and  $D_3$  is turned off.

During  $T_1 < t < T_2$ ,  $V_{DS}$  is clamped to  $2V_G$ .

$$V_{DS} = 2V_G$$

Eq. 2-23

The currents  $i_G$  and  $i_{C1}$  maintain the following relations.

$$i_G = i_{L1} = i_b = -i_{C1} = -i_{L3}$$

Eq. 2-24

(c)  $T_2-T_3$ :

During this time interval,  $V_{DS}$  is reduced in a resonant fashion due to the magnetizing inductance and the output capacitance of the MOSFET, S<sub>1</sub>. V<sub>DS</sub> will be clamped to V<sub>G</sub> because the transformer windings are shorted due to the lack of magnetizing energy. C<sub>1</sub> is charged continuously and V<sub>C1</sub> is clamped to V<sub>G</sub>. Both the voltage stresses on the switch and clamp diode are clamped to the V<sub>G</sub>. At T<sub>3</sub>, the gate drive signal is applied to switching on the switch.

During  $T_2 < t < T_3$ ,  $V_{DS}$  is clamped to  $V_G$ .

$$V_{DS} = V_G$$

Eq. 2-25

The currents  $i_G$  and  $i_{C1}$  maintain the following relations.

$$i_G = i_{L1} = i_b = -i_{C1} = -i_{L3}$$

Eq. 2-26

(d)  $T_3 - T_4$ :

At  $T_3$ , the main switch  $S_1$  is turned on. At T3, the currents maintain the following equations.

$$i_G = i_{L1} = i_b = -i_{C1} = -i_{L3}$$

Eq. 2-27

Due to the turning on of  $D_1$  and  $D_2$ , transformer windings  $P_1$ , P3 and  $L_{s1}$  are shorted. Consequently, both leakage inductances,  $L_1$  and L3, are supplied by a positive voltage and the currents  $i_G$  and  $i_{C1}$  are linearly increased to reflect the demand of the load current.

During  $T_3 < t < T_4$  the currents,  $i_G$  and  $i_{C1}$ , are derived as the following equations.

$$\dot{i}_G = \dot{i}_{L1} = \dot{i}_b + \frac{V_G}{L_1}(t - T_3)$$

, and Eq. 2-28

$$i_{C1} = i_{L2} = -i_b + \frac{V_G}{L_3}(t - T_3)$$

Eq. 2-29

At T<sub>4</sub>,

$$i_G + i_{C1} = i_c + i_a = \frac{i_O}{n}$$

Eq. 2-30

$D_2$  is turned off. The time interval can be calculated as

$$T_4 - T_3 = \frac{L_1 L_3}{V_G (L_1 + L_3)} \frac{i_o}{n}$$

Eq. 2-31

The time interval,  $T_3$ - $T_4$ , becomes the time delay between the time to turn on the MOSFET in the primary winding and the time to apply voltage on the secondary winding of the transformer. This time interval to the switching period is defined as the duty cycle loss in the converter operation. It will affect the load regulation resulting in reducing the converter efficiency.

(e)  $T_4$ - $T_0$ :

The power is transferred from the input source,  $V_G$ , and  $V_{C1}$ . The input voltage is applied on winding  $P_1$ , and  $V_{C1}$  is applied on winding P3. Therefore,  $i_{C1}$  provides part of load current via P3 while  $i_G$  provides the complementary part of the load current via  $P_1$  so that their sum is equal to the reflected load current as the following equation.

$$i_G + i_{C1} = \frac{i_O}{n}$$

Eq. 2-32

At  $T_0$ ,  $S_1$  is turned off and another switching cycle begins.

#### 2.5. Input Current Ripple Reduction

Without an effective solution, adding an external LC filter is used to solve the problems caused by the pulsating input current of the FAC. In contrast, the current ripple reduction feature of the FRR alleviates these problems. Before this research work, no single-switch forward converter had been proposed to be able to reduce the input current ripple without adding an external LC filter.

Eq. 2-12 and Eq. 2-13 are the equations of the input current ripple of the  $\Delta i_G$  and  $\Delta i_{C1}$ . Building on these equations, several key current and voltage values can be expressed in the following equations.

$$\Delta i_{s1} = (i_O / n)$$

Eq. 2-33

$$\Delta i_G = \frac{L_3}{L_1 + L_3} \frac{i_O}{n}$$

Eq. 2-34

$$\Delta i_{C1} = \frac{L_1}{L_1 + L_3} \frac{i_o}{n}$$

Eq. 2-35

$$\Delta i_{Cin} = \frac{L_3}{L_1 + L_3} \frac{i_o}{n}$$

Eq. 2-36

The clamp capacitor voltage ripple  $\Delta V_{C1}$  can be calculated as the following equation.

$$\Delta V_{C1} = \frac{i_{C1} \cdot \Delta t}{C_1} = \frac{i_a \cdot DT_s}{C_1}$$

Eq. 2-37

Referring to Eq. 2-14,  $\Delta V_{C1}$  can be calculated as the following equation.

$$\Delta V_{C1} = \frac{L_1(1-D)}{L_1 + L_3} \frac{i_o}{n} \frac{DT_s}{C_1}$$

Eq. 2-38

Assuming efficiency  $\eta \cong 1$ ,  $i_{in} = \frac{V_o i_o}{V_i}$ , and  $D = \frac{nV_o}{V_i} \implies i_{in} = \frac{Di_o}{n}$ , the RMS

current of i<sub>Cin</sub> can be derived as the following equation.

During  $0 < t < DT_s$ ,

$$i_{Cin} = i_G - i_{in} = \frac{L_3}{L_1 + L_3} \frac{i_O}{n} (1 - D),$$

Eq. 2-39

During  $DT_s < t < T_s$ ,

$$i_{Cin} = i_G - i_{in} = -\frac{L_3}{L_1 + L_3} \frac{Di_O}{n},$$

Eq. 2-40

The RMS current can be calculated as the following equation.

$$i_{C1(RMS)} = \frac{L_1}{L_1 + L_3} \frac{i_o}{n} \sqrt{D(1 - D)}$$

Eq. 2-41

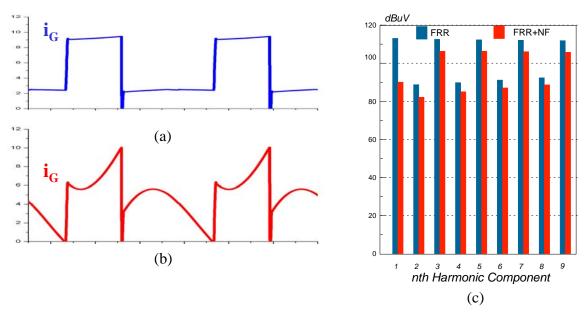

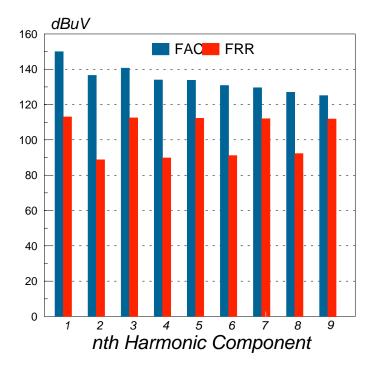

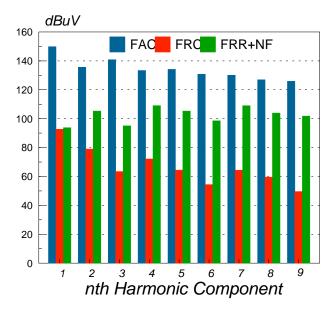

$$i_{Cin(RMS)} = \frac{L_3}{L_1 + L_3} \frac{i_o}{n} \sqrt{D(1 - D)}$$