Werq

-

Постов

12 -

Зарегистрирован

-

Посещение

Тип контента

Профили

Форумы

Блоги

Сообщения, опубликованные Werq

-

-

-

В общем возникает вопрос, что такое narr_sig

0 -

выложу весь код проекта

gen_div

--通用å¶æ•°åˆ†é¢‘器 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity gen_div is generic(div_param:integer:=1); --åˆ†é¢‘å› å,分频为2*div_param,默认2分频 port ( clk:in std_logic;--输入时钟 bclk:out std_logic;--分频输出 resetb:in std_logic--å¤ä½ä¿¡å· ); end gen_div; architecture behave of gen_div is signal tmp:std_logic;--输出暂å˜å¯„å˜å™¨ signal cnt:integer range 0 to div_param:=0;--计数寄å˜å™¨ begin ------------------------------ process(clk,resetb) begin if resetb='1' then --reset有效时,bclk始终是0 cnt<=0; tmp<='0'; elsif rising_edge(clk) then cnt<=cnt+1; if cnt=div_param-1 then tmp<=not tmp;--å–åä¿¡å· cnt<=0; end if; end if; end process; bclk<=tmp;--输出 -------------------------------- end behave;

приемник

--´®¿Ú½ÓÊÕÄ£¿é library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity uart_r is generic(framlen:integer:=8);--Êý¾ÝΪframlen-1 port ( bclkr,resetr,rxdr:in std_logic;--rxdrÊý¾ÝÊäÈë½Å r_ready :out std_logic; rbuf:out std_logic_vector(7 downto 0) ); end uart_r; architecture behave of uart_r is type states is (r_idle,r_sample_start_bit,r_sample_data_bit,r_sample,r_stop); signal state:states:=r_idle; signal rxd_syn:std_logic; signal sim_rxdr:std_logic; begin pro1: process(rxdr)--ÓÃDFF°ÑÊý¾ÝÊäÈë½ÅÕûÐÎÏÂ,·ÀÖ¹¸ÉÈÅ begin if rxdr='0' then rxd_syn<='0'; else rxd_syn<='1'; end if; end process; pro2: process(bclkr,resetr,rxd_syn) variable count :std_logic_vector(3 downto 0); variable rcnt:integer range 0 to framlen :=0; variable rbufs:std_logic_vector(7 downto 0); begin if resetr='1' then state<=r_idle; count:="0000"; rcnt:=0; r_ready<='0'; elsif rising_edge(bclkr) then case state is --j¼ì²âÊÇ·ñÊÇÆðʼλ when r_idle=> if rxd_syn='0' then state<=r_sample_start_bit; r_ready<='0';--¼ì²âµ½Æðʼλºó²Å¸´Î»r_ready rcnt:=0; count:="0000";--ÔÚÕâ¶ùÆðʼλΪ0ÒѾÓÐÒ»¸öʱÖÓʱ¼äÁË else state<=r_idle; end if; when r_sample_start_bit=> --¼ì²âÆðʼλÊÇ·ñ¹»Ê±¼ä if rxd_syn='0' then if count<"0111" then--8¸öʱÖÓºó,ÔÙ²ÉÑù count:=count+1; state<=r_sample_start_bit; else --ÆðʼλÕýÈ·,¿ªÊ¼²ÉÑùÊý¾Ýλ state<=r_sample_data_bit; count:="0000"; rcnt:=0;--¿ªÊ¼½ÓÊÕÊý¾Ýλ end if; else state<=r_idle; count:="0000"; end if; when r_sample_data_bit=> if count<="1110" then--16¸öʱÖÓºóÔÙ²ÉÑù count:=count+1; state<=r_sample_data_bit; else if rcnt=framlen then state<=r_stop; count:="0000"; rcnt:=0; else state<=r_sample_data_bit; count:="0000"; rbufs(rcnt):=rxd_syn;--ÒÆÈëÊý¾Ýλ rcnt:=rcnt+1; end if; end if; when r_stop=> ---Ê¡ÂÔÁ˶ÔֹͣλµÄ¼ì²â r_ready<='1';--½ÓÊÜÊý¾Ý¿É¶ÁÁË rbuf<=rbufs;---¸üÐÂÊä³öÊý¾Ý state<=r_idle; when others=> state<=r_idle; end case; end if; end process; end behave;передачик

--´®¿Ú·¢ËÍÄ£¿é library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity uart_t is generic(framlen:integer:=7);--Êý¾ÝλΪframlen+1λ port ( bclkt,resett,xmit_cmd_p:in std_logic; --bclk-·¢ËÍʱÖÓ£¬reset-¸´Î»ÐźŠ--xmit_cmd_p-ÐÂÒ»ÂÖ·¢ËÍÆô¶¯ÐźŠtxdbuf:in std_logic_vector(7 downto 0); --´ý·¢ËÍÊý¾Ý¼Ä´æÆ÷ txd:out std_logic; --´®ÐÐÊý¾ÝÊä³ö txd_done:out std_logic --Ò»Ö¡Êý¾Ý(8bits)·¢ËÍÍê±Ï±êÖ¾ ); end uart_t; architecture behave of uart_t is type states is (x_idle,x_start_bit,x_data_bit,x_stop_bit); --״̬»ú״̬ signal state:states:=x_idle; --³õʼ״̬Ϊx_idle begin process(bclkt,resett,xmit_cmd_p,txdbuf) variable xcnt16:std_logic_vector(4 downto 0):="00000"; --·¢ËÍ1bitËùÒª±£³ÖµÄʱÖÓ¼ÆÊýÆ÷ --(ÒòΪÏÖÔÚµÄbclktÊÇbaudƵÂʵÄ16±¶) variable xbitcnt:integer range 0 to framlen :=0; --ÒѾ·¢Ë͵ÄÊý¾Ýλ ¼ÆÊýÆ÷ variable txds : std_logic; --´®ÐÐÊä³öÊý¾ÝÔÝ´æ±äÁ¿ begin if resett='1' then state<=x_idle; txd_done<='0'; txds:='1'; xbitcnt:=0; xcnt16:="00000"; elsif rising_edge(bclkt) then case state is when x_idle=> if xmit_cmd_p='1' then ---ÅжÏÊÇ·ñÆô¶¯ÐÂÒ»ÂÖ·¢ËÍ state<=x_start_bit;--×¼±¸·¢ËÍÆðʼλ txd_done<='0';--Ö±µ½ÓÐÕâ¸ö·¢ËÍÂö³åºó,txd_done²Å¸´Î» --´ÓÕâ¶ù¿ªÊ¼,·¢ËÍÊý¾Ý²»ÄܸıäÁË txds:='0'; xcnt16:="00000"; else state<=x_idle; txds:='1'; end if; when x_start_bit=> --·¢ËÍÆðʼλ if xcnt16<="01110" then--ÐèÒª±£³Ö16¸öʱÖÓ xcnt16:=xcnt16+1; txds:='0'; state<=x_start_bit;--¼ÌÐø·¢ËÍÆðʼλ else state<=x_data_bit;--×¼±¸¿ªÊ¼·¢ËÍÊý¾Ýλ xcnt16:="00000";--ÖØÖÃΪ0 txds:=txdbuf(0);--·¢Ë͵Ú0λ xbitcnt:=0; end if; when x_data_bit=> --·¢ËÍÊý¾Ýλ if xcnt16<="01110" then xcnt16:=xcnt16+1; state<=x_data_bit; else if xbitcnt=framlen then --ÅжÏÊÇ·ñÒѾ·¢ËÍÍêÒ»Ö¡(8bits)Êý¾Ý state<=x_stop_bit; xbitcnt:=0; xcnt16:="00000"; txds:='1'; else xbitcnt:=xbitcnt+1; txds:=txdbuf(xbitcnt); state<=x_data_bit; xcnt16:="00000";---ÖØмÆÊýÒ»bitËùÒª±£³ÖµÄʱ¼ä end if; end if; when x_stop_bit=> --ֹͣλҲÊÇ16λ if xcnt16<="01110" then xcnt16:=xcnt16+1; txds:='1'; state<=x_stop_bit; else state<=x_idle; xcnt16:="00000"; txds:='1'; txd_done<='1'; end if; when others=> --»Øµ½x_idle״̬ state<=x_idle; end case; end if; txd<=txds;--µ±txds±ä»¯Ê±,txd¾ÍÁ¢¼´±ä»¯,¹¦ÄÜ·ÂÕæʱÎÞÑÓʱ end process; end behave;

narr_sig

--ÐźÅÕ»¯Æ÷ --ÔÚsig_inµÄÉÏÉýÑØ×÷ΪÆô¶¯Õ»¯µÄÐźŠ--Õ»¯µÄºóµÄÐźųÖÐønarr_prd¸öclkÖÜÆڵĸߵçƽ --µ±narr_prd=0ʱ£¬narr_sig_out¾ÍÊÇ0ÁË library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity narr_sig is port ( sig_in:in std_logic; clk:in std_logic; resetb:in std_logic; narr_prd:in std_logic_vector(7 downto 0);--narrÐźųÖÐøµÄÖÜÆÚÊý(ÒÔclkΪÖÜÆÚ) narr_sig_out:out std_logic ); end narr_sig; architecture behave of narr_sig is signal narr_prd_cnt:std_logic_vector(7 downto 0);--narrÐźųÖÐøµÄÖÜÆÚ¼ÆÊýÆ÷(1->narr_prd) signal stop_narr_flag:std_logic;--Í£Ö¹Õ»¯±êÖ¾0-Õ»¯ 1-²»Õ»¯ begin ------------------------------ narr_sig: process(sig_in,resetb,clk,stop_narr_flag) begin if resetb='1' then narr_prd_cnt<=X"00"; stop_narr_flag<='1'; narr_sig_out<='0'; else if sig_in='0' then narr_prd_cnt<=X"00"; stop_narr_flag<='0'; narr_sig_out<='0'; else if stop_narr_flag='0' then if rising_edge(clk) then narr_prd_cnt<=narr_prd_cnt+'1'; narr_sig_out<='1'; if narr_prd_cnt=narr_prd then stop_narr_flag<='1'; narr_prd_cnt<=X"00"; narr_sig_out<='0'; end if; end if; end if; end if; end if; end process; ---------------------------------- ------------------------------------ end behave;

0 -

В примере есть как минимум 3 дополнительных узла:

1) gen_div - судя по названию это формирователь частоты, возможно с привязанным сбросом.

2) uart_t - передатчик

3) uart_r - приемник.

да, увидел и еще вроде бы narr_sig

А как проще будет, действовать как в примере

или засунуть все в 1 файл?

0 -

Просто все эти приборы нужны, другим людям)) меня же интересует только rs232 и семисегментный индикатор

0 -

Вообще с платой шел вот такой вот код

Но что-то не получается у меня в нем разобраться

Были бы читаемые комментарии

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity top is port ( clkin:in std_logic;--clkin=40M resetin: in std_logic; rxd:in std_logic;--дёІиЎЊиѕ“е…Ґж•°жЌ® --led:out std_logic_vector(2 downto 0);--led控制 txd:out std_logic--дёІиЎЊиѕ“е‡єж•°жЌ® ); end top; architecture behave of top is component gen_div is--е€†йў‘е…ѓд»¶и°ѓз”ЁеЈ°жЋ generic(div_param:integer:=156);--312分频的,дє§з”џ16*9600зљ„ж—¶й’џ port ( clk:in std_logic; bclk:out std_logic; resetb:in std_logic ); end component; component uart_t is--дёІеЏЈеЏ‘йЂЃе…ѓд»¶и°ѓз”ЁеЈ°жЋ port ( bclkt,resett,xmit_cmd_p:in std_logic; txdbuf:in std_logic_vector(7 downto 0); txd:out std_logic; txd_done:out std_logic ); end component; component uart_r is--дёІеЏЈжЋҐж”¶е…ѓд»¶и°ѓз”ЁеЈ°жЋ port ( bclkr,resetr,rxdr:in std_logic; r_ready:out std_logic; rbuf:out std_logic_vector(7 downto 0) ); end component; component narr_sig is--дїЎеЏ·зЄ„еЊ–е…ѓд»¶и°ѓз”ЁеЈ°жЋ port ( sig_in:in std_logic; clk:in std_logic; resetb:in std_logic; narr_prd:in std_logic_vector(7 downto 0);--narrдїЎеЏ·жЊЃз»зљ„е‘Ёжњџж•°(以clkдёєе‘Ёжњџ) narr_sig_out:out std_logic ); end component; ---------------------------------------------------------- signal clk_b:std_logic;--16倍的波特率时钟 --еЏ‘йЂЃз›ёе…іеЇ„ее™Ё-- signal xmit_p:std_logic;--ж–°дёЂиЅ®еЏ‘йЂЃеђЇеЉЁдїЎеЏ· signal xbuf: std_logic_vector(7 downto 0);--еѕ…еЏ‘йЂЃж•°жЌ®зј“е†ІеЊє signal txd_done_iner:std_logic;--дёЂеё§ж•°жЌ®еЏ‘йЂЃе®ЊжЇ•ж ‡еї— --接收相关寄ее™Ё-- signal rev_buf: std_logic_vector(7 downto 0);--接收数据缓冲区 signal rev_ready:std_logic;--дёЂеё§ж•°жЌ®жЋҐж”¶е®ЊжЇ•ж ‡еї— --led 控制-- signal led_tmp:std_logic_vector(2 downto 0); ------------------------------------------------------------ begin uart_baud: gen_div port map--分频模块例化 ( clk=>clkin, resetb=>not resetin, bclk=>clk_b ); ---------- uart_transfer: uart_t port map--дёІеЏЈеЏ‘йЂЃжЁЎеќ—дѕ‹еЊ– ( bclkt=>clk_b, resett=>not resetin, xmit_cmd_p=>xmit_p, txdbuf=>xbuf, txd=>txd, txd_done=>txd_done_iner ); uart_receive: --串口接收元件例化 uart_r port map ( bclkr=>clk_b, resetr=>not resetin, rxdr=>rxd, r_ready=>rev_ready, rbuf=>rev_buf ); narr_rev_ready: --зЄ„еЊ–rev_readyдїЎеЏ·еђЋз»™xmit_p narr_sig port map ( sig_in=>rev_ready,--иѕ“е…ҐйњЂзЄ„еЊ–дїЎеЏ· clk=>clk_b, resetb=>not resetin, narr_prd=>X"03",--narrдїЎеЏ·й«з”µе№іжЊЃз»зљ„е‘Ёжњџж•°(以clkдёєе‘Ёжњџ) narr_sig_out=>xmit_p--иѕ“е‡єзЄ„еЊ–еђЋдїЎеЏ· ); -------------------------- --led<=led_tmp; -------------------------- r_t_data: --把接收到的数据发送出去 process(rev_ready,resetin,rev_buf,led_tmp,clk_ begin if resetin='0' then--е¤ЌдЅЌж—¶е…ЁзЃ --led_tmp<="000"; else if rising_edge(rev_ready) then xbuf<=rev_buf;--иЈ…иЅЅж•°жЌ® --led_tmp<=not led_tmp; end if; end if; end process; ---------------------------------------------------------- end behave;

0 -

Вот делается все это на cyclone FPGA

0 -

Да , сейчас скину

0 -

Я не знаю что Вы будете использовать, возможно на плате стоит настоящий преобразователь uart-RS232, а возможно что uart-usb.

На плате стоит RS-232 + MAX323

0 -

Первое что надо сделать - разобраться с интерфейсом RS232.

Сейчас как раз этим и занимаюсь

Далее нужно определиться с ПО на стороне ПК, что будете использовать? Простой терминал, или самописную программу на языке высокого уровня?

Самописную программу думаю использовать.

Как в ПО будут вводиться данные для отправки в плис?

Вот это тоже интересующий меня вопрос, как сделать грамотнее или удобнее я не знаю(

Куда будут выводиться данные от плис?

Ну и наконец, собственно синтез под плис - как реализовать приемник и передатчик. Как сделать модуль для индикатора.

Данные наверное обратно в программу

С модулем индикатора, проблем возникнуть не должно, т.к. когда-то делал что-то, нужно только вспомнить

А как реализовать приемник и передатчик совсем не знаю(

Если не секрет, почему AHDL? Этот язык исключительно Alter'ы, на нем конечно можно многое сделать, но он не универсален.

Так сложилось что начал знакомство с программированием ПЛИС на нем. А какой язык использовать лучше?

Благодарю за ответ.

0 -

Интерфейс RS232

Необходимо разработать ПО для реализации протокола обмена между ПЛИС и ПК(на прием и передачу)

Прием : ПЛИС должна принимать десятичное число (от 0-9) и передавать его на семисегментный индикатор для контроля

Передача: возврат полученного десятичного число (от 0-9)

Все это нужно сделать на AHDL

Подскажите с чего начать, как и что вообще делать

Знаком с AHDL очень посредственно

0

0

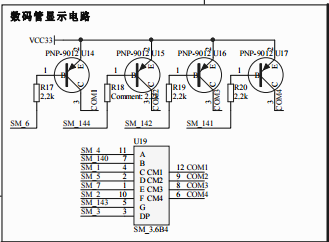

Управление Семи Сегментным Индикатором С Динамическим Управлением

в ПЛИС

Опубликовано

у меня возникла проблема с отображением 2х чисел одновременно. не могли бы вы мне подсказать как это делать?