Icedevil777

-

Постов

11 -

Зарегистрирован

-

Посещение

Тип контента

Профили

Форумы

Блоги

Сообщения, опубликованные Icedevil777

-

-

0

-

15 часов назад, Vascom сказал:

Нет лицензии на IP. Что странно.

На первом рисунке синим цветом выделена лицензия для IP core NCO, но она не работает в железе. Как решить этот вопрос? у кого есть другая лицензия?

0 -

10 минут назад, Vascom сказал:

А в чём проблема? Просто имя файла не нравится?

Time_limited означает, что не смотря на наличие лицензии мега функция будет работать ограниченное время.

0 -

-

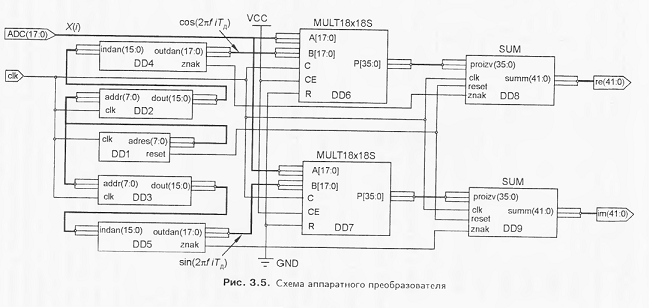

В книге Тарасова Потехина: Разработка систем цифровых сигналов на база ПЛИС на 73 странице описывается самый простой алгоритм, что я нашел, но без объяснения многих вещей.

С сумматорами (DD8,DD9), умножителями(DD6 DD7) и сo cчетчиком(DD1) все понятно в книги даже приведены их VHDl коды.

Помогите разобраться с DD2 DD3 на них нету кодов, их описывают как ПЗУ в которых хранятся таблици косинусов(DD2) и синусов(DD3) .

Еще в книге даны эти графики в качестве подсказки, но почему то для sin отдельного графика нет.

И теперь вопросы:

1 Как можно умножая на значения Сos и Sin получить спектр сигнала?

2 Я рассматривал много примеров, везде говорилось об операции "бабчока" это она и есть или как?

3 В источниках пишут БПФ по 8 / 16 / 64 /1024 точкам а у нас то что?

4 Подскажите как все - таки написать блоки DD2 DD3

5 Допустим я сделаю блоки DD2 DD3 мне нужно выход реальный выход сумматора подать на ЦАП и я сразу получу спектр синусоиды которая идет с АЦП ?

0 -

Передо мной стоит задача реализовать БПФ на ПЛИС на VHDL, многие скажут, что в гугле миллион разных вариантов, я за два дня поисков не нашел подходящий вариант, т.к. основная честь "самописных ядер" очень сложна для понимания, другая часть заточена под Xsilinx, где все время идет речь о встроенных блоков умножения и памяти. Еще много простых кодов, но совсем без описания. Или варианты описаны очень абстрактно, а у меня есть конкретная задача имеется АЦП 12 бит и Cyclone 3. Я формирую синусоиду с выхода ЦАП она идет на АЦП затем необходимо преобразовать ее в СПЕКТР. Нужно сделать максимально маленький и простой проект, но главное с ПЛИС вывести спектр на 2й ЦАП и на осциллограф.

Может кто подскажет хорошую книгу, или есть готовые решения, но с хорошим описанием.

0 -

У меня есть проект Генератор синусоид разных частот -> ЦАП -> АЦП-12 бит -> простой КИХ фильтр ( могу сделать от 30 до 60 коэфф и 29 - 59 регистров) -> ЦАП.

Я сделал ФНЧ. Минимальная частота работы АЦП и она же частота дискретизации фильтра 0.2 мГц. В этом случае фильтр пропускает частоты в диапазоне от 0 до 0.2мГц / 60 = 3.333 Гц, все что выше подавляет. Коэффициенты я не рассчитывал в матлабах и других программа я построил график синусойды разделил ее на 60 отсчетов и получились мои коэффициенты изображены на графике.

Так же получался ФНЧ, который подавляет частоту выше 300 Гц, но для этого пришлось уменьшить частоту дескретизации , т.к. АЦП не может работать медленнее 0.2мГц пришлось брать не все отсчеты от АЦП, а один из десяти или еще меньше, вот сперва я хотел узнать правильно ли я сделал или есть возможность выделить частоту 300 Гц не уменьшая частоту дескритизации фильтра ?

Главный вопрос, а как мне сделать из моего проекта ФВЧ или полосовой фильтр ? Коэффициенты другие брать? или может у меня фильтр не правильно работает? коды VHDL прилагаются.

0

0 -

49 минут назад, Vascom сказал:

Просто переведи числа с твоего АЦП из прямого кода в двоичный дополнительный. И затем результат фильтрации можешь обратно в прямой код перевести для вывода на ЦАП.

Отсюда вытекает два вопроса, каким способом лучше и проще перевести и если такая запись имеет место быть: k17 <= conv_std_logic_vector(2047,12); САПР понимает что это прямой код или дополнительный ?

0 -

Только что, TDA сказал:

Не надо так делать:) фильтр станет совсем другим. Значения АЦП допустим беззнаковые приходят и ползут по линии задержки, но операции умножения на коэффициенты уже знаковые, разрядность результата = Разрядность АЦП + разрядность коэффициентов + знак. Суммирование то же должно быть знаковое. Лучше привести все арифметике с целыми байтами 2 байта значения АЦП, 4 байта результат умножения, 4 байта результат суммирования и далее урезаем лишнее для выхода на ЦАП.

А ЦАП только прямой код понимает, как я фильтрованный сигнал превращу в аналоговый вид? Вот как выглядит ЦАП ШИМ фильтр + прога в ПЛИС.

Если на шим приходит все 11111 до это Umax, если 0 то Umin. Если только научить этот шим понимать отрицательные числа...... но как?

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity shim is port ( clk : in std_logic; r: in integer range 0 to 16383 ; q : out integer range 0 to 16383 ); end entity; architecture rtl of shim is begin process (clk) variable cnt : integer range 0 to 16383; begin if (rising_edge(clk)) then cnt := cnt + 1; end if; if (cnt < r) then q <= 1; else q <= 0; end if; end process; end rtl;0 -

Здравствуйте, У меня есть плата HELPER LMD-System c АЦП, ЦАП(в виде шим фильтра), cyclon 3.

Я новичок в этом деле делаю первый серьезный проект. Цель проекта научиться рассчитывать и создавать цифровые фильтры, а так же работать с ними.

Мой проект состоит из: Генератора синусоиды, с регулятором частоты(от 200Гц до 5кГц), состоит из счетчиков, которые подают меняющийся по кругу двоичный код на ШИМ, а он создает аналоговый сигнал - синусоиду в положительной области. Далее Аналоговый сигнал поступает на вход АЦП-12 бит, снова преобразуется в двоичный код, затем поступает на ЦАП (2й канал ШИМ фильтра). Моя задача поставить фильтр между АЦП и ЦАП, который будет, например пропускать частоты ниже 1кГц, а все что выше задавливать.Суть проблемы: когда я рассчитываю ких фильтр, в матлабе, фиркомпиллере, либо на сайтах онлайн, мне выдают коэффициенты типа:

-41

-120

-125

-22

105

68

-116

-175

130

637

890

637

130

-175

-116

68

105

-22

-125

-120

-41Они отрицательные! У меня АЦП выдает только прямой код, ЦАП, так же понимает только положительный код! У меня одна идея в голове прибавить к этой последовательности цифр 175, чтобы самое маленькое отрицательное превратить в 0! Когда я это сделал мой фильтр начал задавливать в 0 вообще все частоты, почему? может мой подход не верный? если у кого-нибудь есть готовый, рабочий фильтр 12 бит на VHDL, поделитесь, для изучения.

Вот код моего фильтра, c другими коэффицентами на них ненужно смотреть:library Ieee; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_Arith.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Mfil is Port ( clk: in std_logic; adc: in std_logic_vector(11 downto 0); f_out: out std_logic_vector(11 downto 0)); end Mfil; architecture Behavioral of Mfil is signal r0, r1, r2, r3, r4, r5, r6, r7, r8, r9, r10, r11, r12, r13, r14, r15, r16, r17, r18, r19, r20, r21, r22, r23, r24, r25, r26, r27, r28, r29, r30, r31, r32, r33: std_logic_vector(11 downto 0); signal k0, k1, k2, k3, k4, k5, k6, k7, k8, k9, k10, k11, k12, k13, k14, k15, k16, k17, k18, k19, k20, k21, k22, k23, k24, k25, k26, k27, k28, k29, k30, k31, k32, k33, k34: std_logic_vector(11 downto 0); signal p0, p1, p2, p3, p4, p5, p6, p7, p8, p9, p10, p11, p12, p13, p14, p15, p16, p17, p18, p19, p20, p21, p22, p23, p24, p25, p26, p27, p28, p29, p30, p31, p32, p33, p34: std_logic_vector(26 downto 0); signal pl0, pl1, pl2, pl3, pl4, pl5, pl6, pl7, pl8, pl9, pl10, pl11, pl12, pl13, pl14, pl15, pl16, pl17, pl18, pl19, pl20, pl21, pl22, pl23, pl24, pl25, pl26, pl27, pl28, pl29, pl30, pl31, pl32, pl33, pl34: std_logic_vector(23 downto 0); signal sum: std_logic_vector(26 downto 0); begin k0 <= conv_std_logic_vector(45,12); k1 <= conv_std_logic_vector(29,12); k2 <= conv_std_logic_vector(0,12); k3 <= conv_std_logic_vector(-34,12); k4 <= conv_std_logic_vector(-59,12); k5 <= conv_std_logic_vector(-64,12); k6 <= conv_std_logic_vector(-43,12); k7 <= conv_std_logic_vector(0,12); k8 <= conv_std_logic_vector(53,12); k9 <= conv_std_logic_vector(96,12); k10 <= conv_std_logic_vector(110,12); k11 <= conv_std_logic_vector(79,12); k12 <= conv_std_logic_vector(0,12); k13 <= conv_std_logic_vector(-119,12); k14 <= conv_std_logic_vector(-258,12); k15 <= conv_std_logic_vector(-387,12); k16 <= conv_std_logic_vector(-478,12); k17 <= conv_std_logic_vector(2047,12); k18 <= conv_std_logic_vector(-478,12); k19 <= conv_std_logic_vector(-387,12); k20 <= conv_std_logic_vector(-258,12); k21 <= conv_std_logic_vector(-119,12); k22 <= conv_std_logic_vector(0,12); k23 <= conv_std_logic_vector(79,12); k24 <= conv_std_logic_vector(110,12); k25 <= conv_std_logic_vector(96,12); k26 <= conv_std_logic_vector(53,12); k27 <= conv_std_logic_vector(0,12); k28 <= conv_std_logic_vector(-43,12); k29 <= conv_std_logic_vector(-64,12); k30 <= conv_std_logic_vector(-59,12); k31 <= conv_std_logic_vector(-34,12); k32 <= conv_std_logic_vector(0,12); k33 <= conv_std_logic_vector(29,12); k34 <= conv_std_logic_vector(45,12); process (clk) begin if clk'event and clk = '1' then r0 <= adc; r1 <= r0 ; r2 <= r1 ; r3 <= r2 ; r4 <= r3 ; r5 <= r4 ; r6 <= r5 ; r7 <= r6 ; r8 <= r7 ; r9 <= r8 ; r10 <= r9 ; r11 <= r10 ; r12 <= r11 ; r13 <= r12 ; r14 <= r13 ; r15 <= r14 ; r16 <= r15 ; r17 <= r16 ; r18 <= r17 ; r19 <= r18 ; r20 <= r19 ; r21 <= r20 ; r22 <= r21 ; r23 <= r22 ; r24 <= r23 ; r25 <= r24 ; r26 <= r25 ; r27 <= r26 ; r28 <= r27 ; r29 <= r28 ; r30 <= r29 ; r31 <= r30 ; r32 <= r31 ; r33 <= r32 ; sum(26 downto 0) <= p0 + p1 + p2 + p3 + p4 + p5 + p6 + p7 + p8 + p9 + p10 + p11 + p12 + p13 + p14 + p15 + p16 + p17 + p18 + p19 + p20 + p21 + p22 + p23 + p24 + p25 + p26 + p27 + p28 + p29 + p30 + p31 + p32 + p33 + p34 ; end if; end process; p0 <= "000" & pl0 ; p1 <= "000" & pl1 ; p2 <= "000" & pl2 ; p3 <= "000" & pl3 ; p4 <= "000" & pl4 ; p5 <= "000" & pl5 ; p6 <= "000" & pl6 ; p7 <= "000" & pl7 ; p8 <= "000" & pl8 ; p9 <= "000" & pl9 ; p10 <= "000" & pl10 ; p11 <= "000" & pl11 ; p12 <= "000" & pl12 ; p13 <= "000" & pl13 ; p14 <= "000" & pl14 ; p15 <= "000" & pl15 ; p16 <= "000" & pl16 ; p17 <= "000" & pl17 ; p18 <= "000" & pl18 ; p19 <= "000" & pl19 ; p20 <= "000" & pl20 ; p21 <= "000" & pl21 ; p22 <= "000" & pl22 ; p23 <= "000" & pl23 ; p24 <= "000" & pl24 ; p25 <= "000" & pl25 ; p26 <= "000" & pl26 ; p27 <= "000" & pl27 ; p28 <= "000" & pl28 ; p29 <= "000" & pl29 ; p30 <= "000" & pl30 ; p31 <= "000" & pl31 ; p32 <= "000" & pl32 ; p33 <= "000" & pl33 ; p34 <= "000" & pl34 ; pl1 <= r0 * k1 ; pl2 <= r1 * k2 ; pl3 <= r2 * k3 ; pl4 <= r3 * k4 ; pl5 <= r4 * k5 ; pl6 <= r5 * k6 ; pl7 <= r6 * k7 ; pl8 <= r7 * k8 ; pl9 <= r8 * k9 ; pl10 <= r9 * k10 ; pl11 <= r10 * k11 ; pl12 <= r11 * k12 ; pl13 <= r12 * k13 ; pl14 <= r13 * k14 ; pl15 <= r14 * k15 ; pl16 <= r15 * k16 ; pl17 <= r16 * k17 ; pl18 <= r17 * k18 ; pl19 <= r18 * k19 ; pl20 <= r19 * k20 ; pl21 <= r20 * k21 ; pl22 <= r21 * k22 ; pl23 <= r22 * k23 ; pl24 <= r23 * k24 ; pl25 <= r24 * k25 ; pl26 <= r25 * k26 ; pl27 <= r26 * k27 ; pl28 <= r27 * k28 ; pl29 <= r28 * k29 ; pl30 <= r29 * k30 ; pl31 <= r30 * k31 ; pl32 <= r31 * k32 ; pl33 <= r32 * k33 ; pl34 <= r33 * k34 ; f_out(11 downto 0) <= sum (26 downto 15) + "000111011110" ; end architecture; [/HTML]Может у меня сам фильтр не правильно сделан? или разрядность sum после сложения нужно увеличить?

-1

Проблема в отладке проекта

в ПЛИС

Опубликовано

Я занимаюсь ПЛИС уже 2 года, и дошел до сложных проектов, которые просто так не работают на больших частотах.

Вот так выглядит мой проект, он реализует управление РЛС, посредством различных интерфейсов. Его центром является система ЦОС состоящая из КИХ фильтра и NCO, все написано на Verilog.

У меня возникла проблема, на выходе NCO (управляемый генератор синуса) и Фильтра вылезают помехи. Если отделить систему ЦОС от всего проекта, то помехи мне удавалось убрать, я задерживал clk идущий на NCO на 333ps и все отлично работало, в большом проекте я не могу подобрать задержку.

Если с АЦП подать сигнал на фильтр, то на выходе фильтра он будет с помехами. Если снимать сигнал с NCO, то помехи так же присутствуют. Как они выглядят я записал на видео. Бывало, что помехи на фильтре пропадали, а на NCO появлялись и наоборот.

Я понимаю, что проблемы в задержке сигнала, но я никогда не работал с Timing Analysis и не знаю с чего начать. Подскажите как решаются такие проблемы?